ASI总线

ASI(Actuator-Sensor-Interface)是执行器-传感器-接口的英文缩写,它是一种用在控制器(主站)和传感器/执行器(从站)之间双向交换信息的总线网络,它属于现场总线(Fieldbus)下面底层的监控网络系统。

ASI总线基本信息

| 中文名称 | 执行器-传感器-接口 | 外文名称 | Actuator-Sensor-Interface |

|---|---|---|---|

| 简称 | ASI总线 | 类型 | 总线网络 |

在ASi总线系统中,主站和从站之间采用了串行双向数字通信方式。因为报文较短,如若在有一个主站和31个从站的系统中,ASI的通信周期大约为5ms,也就是说主站在5ms内就可以对31个从站轮流访问一遍。

ASI总线造价信息

ASi总线是一个主从系统,主站和所有的从站可双向交换信息,当主站与上层现场总线进行通信时,主站担当了AS-i和上层网络信息交换的出入口,因ASi主要传输的是开关量,所以它的数据结构比较简单,用户仅需关心数据格式、传输率和参数配置等。

一个ASI总线系统通过它主站中的网关可以和多种现场总线(如FF、Profibus、CANbus)相连接。ASi主站可以作为上层现场总线的一个节点服务器,在它的下面又可以挂接一批ASi从站。ASi总线主要运用于具有开关量特征的传感器和执行器系统,传感器可以是各种原理的位置接近开关以及温度、压力、流量、液位开关等。执行器可以是各种开关阀门,电/气转换器以及声、光报警器,也可以是继电器、接触器、按钮等低压开关电器。当然AS-i总线也可以连接模拟量设备,只是模拟信号的传输要占据多个传输周期。必须注意的是在连接主站和从站的两芯电缆上除传输信号外,同时还提供工作电源。

ASI总线常见问题

-

DSP芯片TMS320F2812 DSP片外扩展 64K * 16位SRAM(基本配置),最大可扩展到512K * 16位。内部RAM不够用时,用来扩充内存,当然是并行的。

-

总线制是2根线控制很多根,多线制是每个控制点都有单独的线

-

串行就是数据一位一位传输的,数据线只需要一根(如果支持双向需要2根),并行就是数据多位同时传输(4位,8位,甚至64位,128位),当然效率是并行很高,但是如果远距离传输的话串行成本低。所以,一般设备...

在ASi总线不同的应用情况下,功能可靠包含下列内容,首先是通信数据的可靠性方面,ASi总线在许多方面采取了抗干扰措施。在接收数据时,必须进行错误检验,此方法十分有效,出错误后信息可以重发。另外如系统部件出现故障时主站会很快检测到故障信息,并自动与发生故障的从站切断通信联系,通知操作人员故障地址,以便及时进行维修。主站还具备网络运行监视功能,在任何时刻用户都能得到系统中所有从站当前运行状态的完整资料。

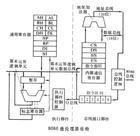

ASI(Actuator-Sensor Interface)是用于在控制器(主站)和传感器/执行器(从站)之间进行双向、多站点数字通信的总线网络,它由主站、从站、传输系统3部分组成,而传输系统又由两芯传输电缆、ASI电源和数据解耦电路构成。

传输电缆

ASI总线推荐使用的电缆型号为CENELEC或DIN VDE 0281[CENE-90],并且要标明HO5VV-F2x1.5,这是一种两芯、横截面积为1.5mm2的柔性电源线,它既便宜又随处可见。另一种是具有相同电特性的ASI专用扁平电缆,它在安装上非常方便。因为ASI电缆既要传输信号又是要提供电源,所以在选择电缆时必须注意两个方面的技术指标:第一是通信频谱特性,第二是直流阻抗特性。在认为有较大干扰的情况下,则需要选择使用屏蔽电缆,如型号为(N)YMHCY-02x1.5的电缆,但它也必须满足规定的频谱特性要求。特别要注意的是屏蔽层在ASI电源端只能接地,而不能接在ASI+和ASI-端。

ASI电源的电压为29.51-31.5VDC,每个从站向传感器/执行器提供的电源电压VDC(+10[%]或-15[%])。在一个ASI总线系统中,ASI电源可给31个从站提供的最大电流为2A,因此每个从站平均消耗的电流为65mA。如果从站带动的执行器功率较大,所需电流大于65mA时,则必须外接辅助电源。整个系统允许在ASI电缆上的最大压降为3V,因此电缆的横截面积不能小于1.5mm2,这样才能保证网络中每个从站都能得到规定的电压值。

ASI电缆的等效电路模型,分为两芯电缆和带屏蔽层两芯电缆两种模型。电阻(R')、电容(C')、电感(L')和电导(G')值为ASI电缆的等效参数。传输速率为167Kb/s时,两芯电缆总的极限参数范围为:R'=20-50mΩ/m,L'=200-600nH/m,C'=35-70pF/m,G'=1-3μS/m。在同样的传输速率下,带屏蔽层的两芯电缆的极限参数为:R's=10mΩ/m,Ls'=800nH/m,Cs'=300pF/m,Gs'=15μS/m。

ASI电缆的复数阻抗与传输速率之间的关系对系统的响应特性具有十分重要的意义。在传输速率为167Kb/s时,阻抗为80-120Ω,而低于或高于167Kb/s时,阻抗会迅速下降,因此当采用167Kb/s的传输速率时,将得到最大的信号幅值。

信号调制过程

ASI信号在传输前要进行调制,采用什么调制方法要考虑诸多的因素。例如附加在电源电压上的传输信号必须是交变的;主站和从站之间的双向通信要求双主都能够产生简单、有效和节省时间的窄带传输信号;使用非屏蔽电缆时不应有太多的干扰等等。ASI信号的调制采用交变脉冲调制方式(APM),这是一种在基频进行调制的串行通信方式。

主站发出的请求信号位序列首先转换为能执行相位变换的位序列,即曼彻斯特II编码,这样就产生了相应的传输电流。当传输电流通过电感元件时会产生电压突变,就产生了请求信号电压。每一个增加的电流产生一个负电压脉冲,而每一个减小的电流产生一个正电压脉冲,通过这种方法从站很容易得到请求信号。因为信号是叠加在电源上的,所以信号电压有时会大于从站的电源电压。在从站内并不需要电感元件,这就使得智能型传感器/执行器上的带有Slave Chip元件的一体化从站电路更小、更简单、更经济。在从站中接收电缆上的请求信号电压并转化为初始的位序列,就完成了一次主站向从站的请求信号的转换过程。

信号传输的电压脉冲被设计成正弦平方波方式,但要考虑到低频干扰的影响,通过选择合适的传输波形可以提高可靠性。经过这种调制后的信号在规定的拓扑结构中,每两位脉冲信号的间隔只有6μs。

电源和数据解耦

ASI电源和与之相连的数据解耦电路,ASI电源可以提供29.5-31.6VDC电压,完全满足国际电工委员会(IEC)对安全隔离低电压的技术要求,并具有可靠的短路过载保护。数据解耦电路由两个50μH的电感和两个39Ω的电阻相互并联组成,通过电感可以将传输信号的电流脉冲转变为电压脉冲,同时它还具有防止数据传输频率信号经过电源而造成短路的作用,两个电阻代表了网络的边界终端。为使电路信号噪声最低,必须采用高对称性的电路结构,两个电容CE和两个电感L应完全相等,接地点要可靠接地,若采用屏蔽电缆,屏蔽层也应接到地上。如果2A电流仍不能满足从站的要求,就必须采用带有辅助电源的从站模式或使用带有附加电源的中继器。

访问方式和报文

ASI总线系统为主从结构,采用请求-应答的访问方式。主站先发出一个请求信号,信号中包括从站的地址。接到请求的从站会在规定的时间内给予应答,在任何时间只有1个主站和最多31个从站进行通信。一般访问方式有两种:一种是带有令牌传递的多主机访问方式;另一种是CSMA/CD方式,它带有优先级选择和帧传输过程。而ASI的访问方式比较简单,为了降低从站的费用、提高灵活性,一方面在不增加传输周期的条件下尽量包括更多的参数和信息,另一方面传输周期的时间应能自动调整,例如系统中只有6个从站时,传输周期为1ms,而有31个从站时周期约为5ms。如果在网上有短暂的干扰时,主站没有收到从站的应答信号或收到的是错误无效的信号时,主站可以重发信息而无需重复整个传输周期。

ASI总线的总传输速率为167Kb/s,它包括所有功能上必要的暂停。允许的网络传输速率为53.3Kb/s,从这一点看它的传输效率为32[%],与其它现场总线系统相比,这个数值较好。但在电磁干扰的环境下应采取进一步措施,以保证数据传输的可靠性。

一个ASI报文由主站请求、主站暂停、从站应答和从站暂停4个环节组成。所有的主站请求都是14位,从站应答为7位,每一位的时间长度为6μs。主站暂停最少为3位,最多为10位。如果从站是同步的话,在主站3位暂停后从站就可以发送应答信号。如果不是同步信号,那么从站就必须在5位暂停后发送应答信号,因为在这段时间内从站会在接收到完整有效的请求信号后监测主站的暂停情况,看看是否还会有其它信息。但是如果主站在10个暂停位后没有接收到从站的应答信号的起始位,主站会认为不再有应答信号而发出下一个地址的请求信号。从站的暂停只有1位或2位的时间。

在ASI报文中主站请求由以下具体信息组成:

ST 起始位 主站请求开始,0为有效,1为无效。

SR 控制位 数据/参数/地址位或命令位,0为数据/参数/地址位,1为命令位。

A0~A4 从站地址位 被访问的从站地址(5位)。

I0~I4 信息位 要传输的信息(5位),请求类型。

PB 奇偶校验位 在主站请求信息中不包括结束位为1的各位总和必须是偶数。

EB 结束位 请求结束,0为无效,1为有效。

在ASI报文中从站应答由以下具体信息组成:

ST 起始位 从站应答开始,0为有效,1为无效。

I0~I3 信息位 要传输的信息(4位),应答类型。

PB 奇偶校验位 在从站应答信息中不包括结束位为1的各位总和必须是偶数。

EB 结束位 应答结束,0为无效,1为有效。

主站请求和从站应答

在ASI主从结构中,主站所发出的报文在系统数据交换中占有重要的地位。主站的请求报文共有9种:(1)数据交换 要求从站把测量数据上传给主站,而主站又可以把控制指令下达给从站。(2)写参数 设置从站功能,如传感器的测量范围、激活定时器、在多传感器系统中改变测量方法等。(3)地址分配 只有当从站地址为00H时才有效。从站接到这个请求后,用06H回答,表示已收到了主站的正确请求,从站从此就可以在这个新地址被呼叫了,同时把这个新地址存储在从站的EEPROM中,这个过程大约需要15ms。这种方式使主站可以对运行中损坏后重新置换的从站自动进行原有地址的设置。(4)复位 把被呼叫的从站地址恢复到初始状态,从站用06H回答,整个过程需2ms。(5)删除操作地址 暂时把被呼叫的从站地址改为00H,这个报文一般和"地址分配"报文一起使用。当新地址确定后,从站用06H回答。如果使用指令"Reset-ASI-Slave"就可以恢复原地址。(6)读I/O配置。(7)读ID编码 从站的I/O设置和ID编码在出厂时已经确定,不能改变。(6)、(7)结合使用的目的是确定从站的身份。(8)状态读取 读取从站状态缓冲器中的4个数据位,以获得在寻址和复位过程中出现的错误信息。(9)读出状态和状态删除 读出从站状态缓冲器的内容,然后删除。

在以上9种主站请求报文中,数据和参数的传输有两种,设置和改变从站地址的有两种,对从站进行识别和查询的有5种。表1列出的是主站9种报文的名称和内容。

传输故障特征

如果在非屏蔽电缆上进行高速ASI传输通信,那么电磁兼容性(EMC)问题就非常重要了。发射干扰和现场的场强辐射干扰都不应超过欧洲标准EN55011给出极限值,ASI系统的抗干扰能力在IEC801文件中已有详细的说明。大量的ASI系统测试数据表明,由于传输信号采用了正弦平方波,因此ASI系统的发射干扰保持在IEC的规定值以下。ASI系统对于静态放电在26M-1GHz频率范围内的电磁高速瞬间干扰的抵抗能力可达到3级。在最坏的情况下,通信将出现故障,但系统具有检测功能并可以对报文进行重发。因为是短信息,重发不会增加周期时间,只有在报文发生严重错误时,才会增加报文的周期长度。当位传输错误率在70b/s时,系统周期大约为5ms;如果错误率再高一点,周期时间变化不大,ASI仍能保持它所有的功能。只有误差超过5000b/s时,正常的数据传输才难以维持。

当ASI电缆被切断时(如错误短接或故障断开),主站将不能访问位于断点另一侧的从站,而位于主站一侧的从站仍可以被主站呼叫。通过管理服务程序主站能够诊断和发出故障信号,但前提是数据解耦电路和电源这时应在同一侧,否则系统就会完全瘫痪。如果在ASI系统中没有使用中继器,那么当电源发生故障时,ASI系统将停止工作,有关故障的信息也不会得到。但如果使用了中继器,因中继器可以向网络供电,那么电源故障的影响就会减小,系统将维持部分功能。

ASI总线的传输系统是连接网络系统中主站、从站、电源、控制器、传感器/执行器的通路和桥梁。报文信号在传输系统中要经过多次的变换和恢复,并要抵抗各种外界的干扰以保证准确、快捷、可靠的信息交换,它是ASI总线系统中重要的组成部分。

ASI总线文献

现场总线简介及总线电缆的设计

现场总线简介及总线电缆的设计

本文主要介绍了目前工业自动化控制系统中广泛使用的几种现场总线及其总线电缆的特点,并以基金会现场总线FF-H1(低速)和Profibus PA总线电缆为例,探讨了现场总线电缆的设计。

基于PXI总线的MIC总线通讯模块设计

基于PXI总线的MIC总线通讯模块设计

MIC总线是专门为了解决现代军事及工业领域中极其复杂和恶劣的工作环境下电力/数据的分配和管理而开发的一种具有结构简单及高可靠性的现场总线;在详细分析MIC总线的体系结构和通信协议之后,提出了基于PXI总线体系结构的MIC总线通讯模块的软硬件设计方案;系统可通过PXI总线灵活配置MIC的各种通讯模式参数,具有即插即用、高可靠性和小型化易集成等特点;实验证明,主模块PIM工作模式与远程从模块间数据通讯稳定且可靠,对国内MIC总线的研究与应用有重要意义。

系统总线常用总线

ISA总线

----ISA(industrial standard architecture)总线标准是IBM 公司1984年为推出PC/AT机而建立的系统总线标准,所以也叫AT总线。它是对XT总线的扩展,以适应8/16位数据总线要求。它在80286至80486时代应用非常广泛,以至于奔腾机中还保留有ISA总线插槽。ISA总线有98只引脚。

EISA总线

----EISA总线是1988年由Compaq等9家公司联合推出的总线标准。它是在ISA总线的基础上使用双层插座,在原来ISA总线的98条信号线上又增加了98条信号线,也就是在两条ISA信号线之间添加一条EISA信号线。在实用中,EISA总线完全兼容ISA总线信号。

VESA总线

----VESA( video electronics standard association)总线是 1992年由60家附件卡制造商联合推出的一种局部总线,简称为VL(VESA local bus)总线。它的推出为微机系统总线体系结构的革新奠定了基础。该总线系统考虑到CPU与主存和Cache 的直接相连,通常把这部分总线称为CPU总线或主总线,其他设备通过VL总线与CPU总线相连,所以VL总线被称为局部总线。它定义了32位数据线,且可通过扩展槽扩展到64 位,使用33MHz时钟频率,最大传输率达132MB/s,可与CPU同步工作。是一种高速、高效的局部总线,可支持386SX、386DX、486SX、486DX及奔腾微处理器。

PCI总线

----PCI(peripheral component interconnect)总线是当前最流行的总线之一,它是由Intel公司推出的一种局部总线。它定义了32位数据总线,且可扩展为64位。PCI总线主板插槽的体积比原ISA总线插槽还小,其功能比VESA、ISA有极大的改善,支持突发读写操作,最大传输速率可达132MB/s,可同时支持多组外围设备。 PCI局部总线不能兼容现有的ISA、EISA、MCA(micro channel architecture)总线,但它不受制于处理器,是基于奔腾等新一代微处理器而发展的总线。

CompactPCI

----以上所列举的几种系统总线一般都用于商用PC机中,在计算机系统总线中,还有另一大类为适应工业现场环境而设计的系统总线,比如STD总线、VME总线、PC/104总线等。这里仅介绍当前工业计算机的热门总线之一--Compact PCI。

----Compact PCI的意思是"坚实的PCI",是当今第一个采用无源总线底板结构的PCI系统,是PCI总线的电气和软件标准加欧式卡的工业组装标准,是当今最新的一种工业计算机标准。 Compact PCI是在原来PCI总线基础上改造而来,它利用PCI的优点,提供满足工业环境应用要求的高性能核心系统,同时还考虑充分利用传统的总线产品,如ISA、STD、VME或PC/104来扩充系统的I/O和其他功能。

----6.PCI-E总线

----PCI Express采用的也是业内流行这种点对点串行连接,比起PCI以及更早期的计算机总线的共享并行架构,每个设备都有自己的专用连接,不需要向整个总线请求带宽,而且可以把数据传输率提高到一个很高的频率,达到PCI所不能提供的高带宽。相对于传统PCI总线在单一时间周期内只能实现单向传输,PCI Express的双单工连接能提供更高的传输速率和质量,它们之间的差异跟半双工和全双工类似。

系统总线上传送的信息包括数据信息、地址信息、控制信息,因此,系统总线包含有三种不同功能的总线,即数据总线DB(Data Bus)、地址总线AB(Address Bus)和控制总线CB(Control Bus)。

数据总线DB用于传送数据信息。数据总线是双向三态形式(双向是指可以两个方向传输,可以A->B也可以A<-B;三态指 0,1和第三态(tri-state)。tri-state既不是一也不是零,三态门的闭合无输出高阻状态。)的总线,即他既可以把CPU的数据传送到存储器或I/O接口等其它部件,也可以将其它部件的数据传送到CPU。数据总线的位数是微型计算机的一个重要指标,通常与微处理的字长相一致。例如Intel 8086微处理器字长16位,其数据总线宽度也是16位。需要指出的是,数据的含义是广义的,它可以是真正的数据,也可以指令代码或状态信息,有时甚至是一个控制信息,因此,在实际工作中,数据总线上传送的并不一定仅仅是真正意义上的数据。

地址总线AB是专门用来传送地址的,由于地址只能从CPU传向外部存储器或I/O端口,所以地址总线总是单向三态的,这与数据总线不同。地址总线的位数决定了CPU可直接寻址的内存空间大小,比如8位微机的地址总线为16位,则其最大可寻址空间为2^16=64KB,16位微型机的地址总线为20位,其可寻址空间为2^20=1MB。一般来说,若地址总线为n位,则可寻址空间为2^n(2的n次方)个地址空间(存储单元)。 举例来说:一个16位元宽度的位址总线(通常在1970年和1980年早期的8位元处理器中使用)可以寻址的内存空间为 2 的 16 次方=65536=64 KB的地址,而一个 32位元 位址总线(通常在像现今 2004年 的 PC 处理器中) 可以寻址的内存空间为4,294,967,296=4GB(前提:数据总线的宽度是8位)的位址。

注释:位元=bit。

上面提到的2^n=X=YGB中的B其实是bit,这个结果其实是乘以可寻址的位元8bit之后得到的。

控制总线CB用来传送控制信号和时序信号。控制信号中,有的是微处理器送往存储器和I/O接口电路的,如读/写信号,片选信号、中断响应信号等;也有是其它部件反馈给CPU的,比如:中断申请信号、复位信号、总线请求信号、限备就绪信号等。因此,控制总线的传送方向由具体控制信号而定,一般是双向的,控制总线的位数要根据系统的实际控制需要而定。实际上控制总线的具体情况主要取决于CPU。

前端总线总线速率

超频和相关总线速率

中央处理器(CPU)

中央处理器的时钟频率速度(简称内频)由系统总线速率(bus speed)乘上倍频系数决定。例如,一个时钟频率速度为 700MHz 的处理器,可能运行于 100MHz 的系统总线上。这说明处理器内的时钟倍频器的倍率设置为7,即中央处理器被设置为以7倍于系统总线的速率运行:100 MHz×7 = 700 MHz。通过改变倍频系数或系统总线速率,可以得到不同的时钟频率速度。以前经常套用的规则认为:时钟频率速度=外频(前端总线、FSB)*倍频系数。这句话严格来说并不正确。因为现在系统总线、前端总线(外频、FSB)速率不一样。就 Intel CPU 来说,前端总线=系统总线*4。所以,应该说时钟频率速度=系统总线*倍频系数。大多数主板允许用户通过跳线设置(BIOS)设置倍频或系统总线速率。现在许多处理器制造商预先锁定了处理器的倍频,但可以通过某些手段解锁。对所有的处理器,系统总线速率的适当提高可以增进其处理速率。

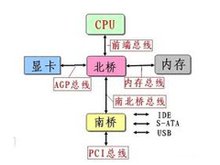

前端总线与系统总线

系统总线(BusSpeed)与前端总线(FSB、外频)的区别在于,前端总线(FSB、外频)的速度指的是CPU和北桥芯片间总线的速度。而系统总线(BusSpeed)的概念是创建在数字脉冲信号震荡速度基础之上的,也就是说,100MHz系统总线(BusSpeed)特指数字脉冲信号在每秒钟震荡一百万次,它更多的影响了PCI及其他总线的频率。之所以前端总线(FSB、外频)与系统总线(BusSpeed)这两个概念容易混淆,主要的原因是在以前的很长一段时间里,前端总线(FSB、外频)与系统总线(BusSpeed)是相同速率,因此往往直接称系统总线(BusSpeed)为外频,最终造成这样的误会。随着电脑技术的发展,人们发现前端总线频率(外频、FSB)需要高于系统总线(BusSpeed),因此采用了QDR(Quad Date Rate)技术,或者其他类似的技术实现这个目的。这些技术的原理类似于AGP的2X或者4X,它们使得的前端总线(FSB、外频)频率成为系统总线(BusSpeed)的2倍、4倍甚至更高,从此之后系统总线(BusSpeed)和前端总线(FSB、外频)的区别才开始被人们重视起来。

- 相关百科

- 相关知识

- 相关专栏

- 不锈钢立式止回阀

- 气动对夹薄型球阀

- 现场总线技术及其应用

- 西安轻轨

- DCS与现场总线控制系统

- Z40WAPI低温法兰闸阀

- 液压密封系统

- CAN总线轻松入门与实践

- PhenixEX系列L37UV滤镜

- 外部总线

- 分条机液压螺母

- CAN总线步进电机驱动器

- 二总线

- DZ41Y低温法兰闸阀

- LIN总线

- profibus总线

- 状态优化的I~2C总线主控制器的FPGA设计

- 简单实用的RS-485总线光电隔离中继器设计

- 基于CAN总线数控系统远程输入输出模块设计与实现

- 基于ARM和CC-Link现场总线工位控制器设计

- 基于CAN总线新型LED信号机状态在线检测设计

- 基于CAN总线和AVR单片机步进电机控制模块设计

- 基于I~2C总线和RS485协议集中通信系统设计

- 基于C8051F040和CAN总线液位控制器设计

- 基于RS485总线技术PC机与单片机多机通讯设计

- 基于RS-485总线主从分布式电阻炉温度群控系统

- 基于Wolfson音频SoCI~2C总线接口设计

- 基于LabVIEWCAN总线通信系统设计与实现

- 基于C8051F040CAN总线中继器设计与实现

- 基于Lon总线节能空调控制系统实现相关技术讨论

- 基于PLC、现场总线化工化合生产线电气自动化改造

- 基于LonWorks总线遥测双向垂线坐标仪设计