闩锁效应

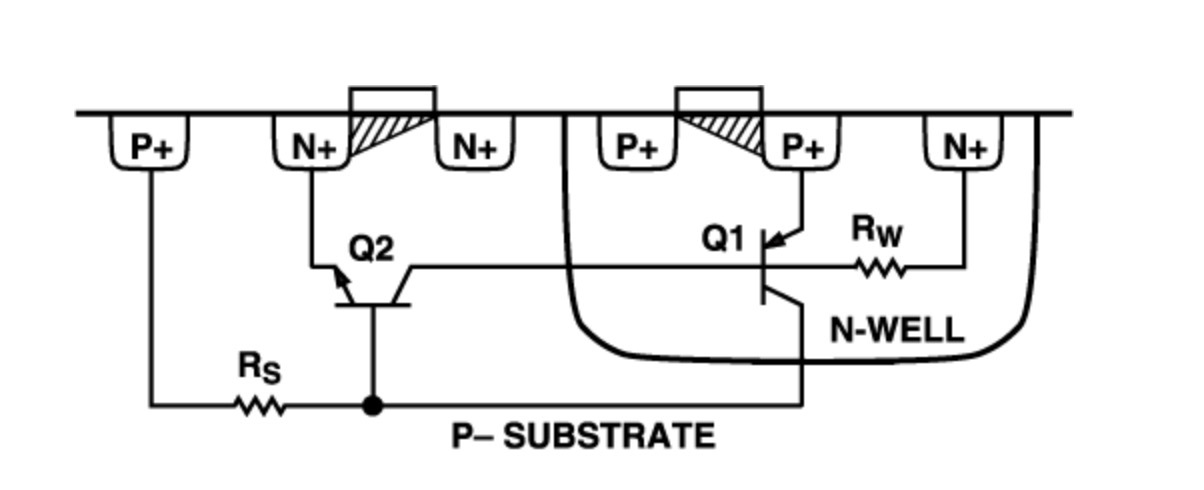

闩锁效应是由NMOS的有源区、P衬底、N阱、PMOS的有源区构成的n-p-n-p结构产生的,当其中一个三极管正偏时,就会构成正反馈形成闩锁。

闩锁效应基本信息

| 中文名称 | 闩锁效应 | 外文名称 | CMOS Latch-up |

|---|---|---|---|

| 结构 | n-p-n-p结构 | 条件 | 当其中一个三极管正偏时 |

| 特色 | 是CMOS工艺所特有的寄生效应 | ||

闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。闩锁效应是由NMOS的有源区、P衬底、N阱、PMOS的有源区构成的n-p-n-p结构产生的,当其中一个三极管正偏时,就会构成正反馈形成闩锁。避免闩锁的方法就是要减小衬底和N阱的寄生电阻,使寄生的三极管不会处于正偏状态。 静电是一种看不见的破坏力,会对电子元器件产生影响。ESD 和相关的电压瞬变都会引起闩锁效应(latch-up),是半导体器件失效的主要原因之一。如果有一个强电场施加在器件结构中的氧化物薄膜上,则该氧化物薄膜就会因介质击穿而损坏。很细的金属化迹线会由于大电流而损坏,并会由于浪涌电流造成的过热而形成开路。这就是所谓的"闩锁效应"。在闩锁情况下,器件在电源与地之间形成短路,造成大电流、EOS(电过载)和器件损坏。

MOS工艺含有许多内在的双极型晶体管。在CMOS工艺下,阱与衬底结合会导致寄生的n-p-n-p结构。这些结构会导致VDD和VSS线的短路,从而通常会破坏芯片,或者引起系统错误。

例如,在n阱结构中,n-p-n-p结构是由NMOS的源,p衬底,n阱和PMOS的源构成的。当两个双极型晶体管之一前向偏置时(例如由于流经阱或衬底的电流引起),会引起另一个晶体管的基极电流增加。这个正反馈将不断地引起电流增加,直到电路出故障,或者烧掉。

可以通过提供大量的阱和衬底接触来避免闩锁效应。闩锁效应在早期的CMOS工艺中很重要。不过,现在已经不再是个问题了。在近些年,工艺的改进和设计的优化已经消除了闩锁的危险。

Latch up 的定义

Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路

Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流

随着IC制造工艺的发展, 封装密度和集成度越来越高,产生Latch up的可能性会越来越大

Latch up 产生的过度电流量可能会使芯片产生永久性的破坏, Latch up 的防范是IC Layout 的最重要措施之一

闩锁效应造价信息

闩锁效应常见问题

-

声波在空气中传播时会产生压力及位移的波动。其实,声波的传播也会引起温度的波动。当声波所引起的压力、位移及温度的波动与一固体边界相作用时,就会发生明显的声波能量与热能的转换,这就是热声效应。 热声效应,...

-

对于这个词的解释听说是有一个故事的,有个故事,一个随意吐痰的人,偶尔到一装修靓丽,铺有地毯的朋友家做客,忽然有痰,但没有痰盂,活生生把痰咽了。这就是所谓地毯效应。环境可以强硬改变习惯。呵呵~

-

你指的光电效应是什么?是爱伊斯坦光电效应吗?如果是大学课程的话,光电效应包含光伏效应。光电效应后很多种,按照是否发射电子,光电效应分为内光电效应和外光电效应,内光电效应包括光电导效应、光伏效应、光子牵...

闩锁效应文献

锁定钢板的应力遮挡效应

锁定钢板的应力遮挡效应

刘振东医师等以个人独到见解,对锁定钢板的应力遮当效应问题,进行了较为详尽的论述,尽管这些观点仅是个人看法,但对目前国内尚处争议的骨折内固定领域有一定借鉴和参考价值,希望广大专家同行就这些问题发表看法,各抒已见,通过学术争鸣,以促进骨折内固定技术规范、健康地发展。

非晶丝GMI效应频率谱和锁相环电路磁场传感器

非晶丝GMI效应频率谱和锁相环电路磁场传感器

采用HP4191A型阻抗分析仪和专门为测量非晶丝GMI效应而设计的专用装置,研究了测量电流频率钴-铁-硅-硼(Co-Fe-Si-B)非晶丝GMI效应的影响。对于经冷拔、真空退火和张应力退火制成的非晶丝,当测量频率由1MHz、5 MHz、10 MHz、20 MHz、30 MHz、40 MHz…,改变到400 MHz时,GMI比值、[(Z-Z0)/Z0]、对外加磁场(Hex)的关系曲线都呈现正GMI效应的特征,其峰值和曲线的最大斜率先是不断增加,直到极大值,然后下降,极大值约为60~100MHz。据此,设计了测量电流频率可变的压控振荡器电路GMI磁场传感器,在75 MHz下,传感器的磁场测量灵敏度达到0.4 mV/nT.

2MHz 单位增益带宽保证

SE4558 的电源电压为 ±22V,NE4558 的电源电压为 ±18V

具备短路保护功能

无需频率补偿

无闩锁效应

宽广的共模和差动电压范围

低功耗

绝对最大额定值

2MHz 单位增益带宽保证

SE4558 的电源电压为 ±22V,NE4558 的电源电压为 ±18V

具备短路保护功能

无需频率补偿

无闩锁效应

宽广的共模和差动电压范围

低功耗

绝对最大额定值

注释:

1. 在超过 25°C 时,按下面的比率递减:

N 型封装为 9.3mW/°C

D 型封装为 6.2mW/°C

2. 当电源电压小于 ±15V 时,绝对最大输入电压等于电源电压。

3. 此处仅指一个运放对地短路。对于 NE4558,额定值适用于 125°C 外壳温度或 75°C 环境温度,对于 SA4558,额定值适用于 85°C 环境温度。

- 相关百科

- 相关知识

- 相关专栏

- 自锁

- 双向差异凝胶电泳

- 自锁现象

- 锁止离合器

- 双向塑料土工格栅

- 双向带动

- 筹码锁定指标

- SP45F数字锁定平衡阀

- 双向四车道

- 数字锁定平衡阀

- 锁颌

- XiR P8668 便携式双向对讲机

- 双层双向钢筋

- 双向板

- 双向晶闸管

- 锁相频率合成器

- 基于压电堆驱动器的喷嘴挡板式气体控制阀

- 电气工程及其自动化特色专业建设探索

- 分形DGS单元结构设计及其在微带电路中的应用

- 磷铵技术改造五大磷肥工程的建议

- 以大豆油多元醇制备的硬质聚氨酯泡沫塑料的性能

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 预制砌块(砖、石)挡土墙工程砌体施工安全技术交底

- 应用模糊数学理论对公路工程建设项目方案的综合评价

- 引嫩工程扩建区土壤水盐动态与防治土壤盐碱措施

- 中华华丹雨、污水管道沟槽开挖专项施工方案教学教材

- 中国工程图学学会成立工程与制造系统集成化分会

- 中国吹制玻璃行业市场前景分析预测年度报告(目录)

- 可替代现有隔热保温材料的新型材料

- 医院病房楼工程施工装饰装修工程施工控制

- 在生活中构筑自然——河南天旺园林工程有限公司剪影

- 中国机械工程学会授予材料热处理工程师资格人员名单