时钟触发器基本信息

| 中文名称 | 时钟触发器 | 外文名称 | clock pulse |

|---|

数字电路中要实现各部分协同工作,需要有统一的时钟脉冲来控制动作,简称为时钟CP,凡是有时钟信号控制的触发器均称为时钟触发器。时钟触发器又可分为同步触发器、主从触发器、边沿触发器。

时钟触发器按逻辑功能分为5种:时钟jk触发器、rs触发器、d触发器、t触发器、t'触发器。

时钟触发器造价信息

时钟触发器常见问题

-

D触发器的状态方程是:Q*=D;jk触发器的状态方程是:Q*=JQ'+K'Q。让两式相等可得:D=JQ'+K'Q。用门电路实现上述函数即可转换成为jk触发器。你看下图就...

-

施密特触发器:电位触发方式,可以控制触发电位。它也有两个稳定状态,但与一般触发器不同的是,施密特触发器采用电位触发方式,其状态由输入信号电位维持;对于负向递减和正向递增两种不同变化方向的输入信号,施密...

时钟触发器文献

低功耗能量回收时钟发生器和触发器的设计

低功耗能量回收时钟发生器和触发器的设计

在深入研究能量回收和门控时钟技术的基础上,提出了能量回收时钟发生器和触发器的新型设计方案。该方案在SMIC0.35μm CMOS标准工艺下,利用Spectre软件进行仿真。仿真结果表明,采用能量回收技术后,新型结构的功耗比传统结构下降约42%;采用门控时钟技术后,新型结构的功耗比传统结构下降约65%。

时钟边沿可控双边沿触发器设计及其应用

时钟边沿可控双边沿触发器设计及其应用

本文设计了时钟边沿可控双边沿触发器,在传统的双边沿触发器内部增加时钟控制电路,实现对单个时钟边沿的控制。同时,提出了基于隔态封锁技术的时序电路设计方法,可封锁时钟信号中所有冗余边沿的触发行为。HSPICE模拟与能耗分析证明,本文设计的电路不仅能够封锁所有的冗余时钟边沿的触发,而且可以简化组合电路部分的设计,从而实现更低的系统功耗。

主从RS触发器概述

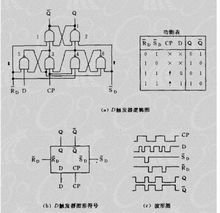

1.电路组成和符号

(注:图中的门全部为与非门)

主从RS触发器电路和逻辑符号如图Z1406所示。其中A、B、C、D门组成的同步RS触发器,称为从触发器;E、F、G、H门组成另一个同步RS触发器,称为主触发器。时钟脉冲CP直接控制主触发器,并通过I门倒相,以 控制从触发器。

2.工作原理

(1)当CP=1即时钟脉冲到来时,G、H门打开,接收R、S端的信号,使主触发器发生动作,由于CP'=0,C、D门被封锁,使从触发器亦即整个触发器保持原状态不变。

(2)当CP=0即时钟脉冲回到低电平时,G、H门被封锁,主触发器不动作,其状态保持不变;由于CP'=1,C、D门打开,接收主触发器原状态信号,使从触发器发生动作,从而导致整个触发器处于某一确定状态。

主从RS触发器状态的翻转发生在CP脉冲的下降沿,即CP由1跳变到0的时刻。在CP=1期间触发器的状态保持不变。因此,来一个时钟脉冲,触发器状态至多改变一次,从而解决了同步RS触发器的空翻问题。

3.主从RS触发器的逻辑功能与同步RS触发器的逻辑功能相同,因此特性表、特性方程、状态图和驱动表也完全相同。

4.主从RS触发器的特点

(1)由两个同步RS触发器即主触发器组成,它们受互补时钟脉冲控制。

(2)触发器在时钟脉冲作用期间接受输入信号,在时钟脉冲的跳变沿允许触发翻转,在时钟跳变后封锁输入信号,因而触发方式属于边沿触发。

触发器的翻转状态由主触发器的状态,即时钟脉冲作用期间输入信号R、S的状态而定。

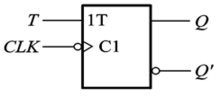

边沿触发器概述

具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。触发器接收的是时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据。常用的正边沿触发器是D 触发器,图2.5 给出了它的逻辑图及典型波形图。

边沿触发器和电位触发器的不同在于:

电位触发器在 E=1 期间来到的数据会立刻被接收。但对于边沿触发器,在CP=1 期间来到的数据,必须"延迟"到该CP=1 过后的下一个CP 边沿来到时才被接收。因此边沿触发器又称延迟型触发器。边沿触发器在CP 正跳变(对正边沿触发器)以外期间出现在D 端的数据变化和干扰不会被接收,因此有很强的抗数据端干扰的能力而被广泛应用,它除用来组成寄存器外,还可用来组成计数器和移位寄存器等。

至于电位触发器。只要 Z 为约定电平,数据来到后就可立即被接收,它不需像边沿触发器那样保持到约定控制信号跳变来到才被接收。

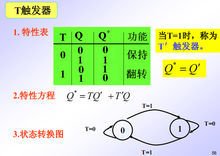

T触发器概述

T触发器,什么是T触发器

T触发器的特性方程

Q * = T Q ' +T ' Q

T触发器的特性表

T | Q | Q* |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

- 相关百科

- 相关知识

- 相关专栏

- JK触发器

- R-S触发器

- 单稳态触发器

- T触发器

- 火种灯

- 三相闭环触发器

- 触发器件

- 永诺闪光灯无线触发器CTR-301P

- 旧青洲灯塔

- 城外诚二手家具市场

- FCC系列磁性触发器

- 激光车灯

- 加密触发器

- 光束灯触发器

- 内部信用增级

- 品色F-508 For Canon 无线闪光灯触发器

- 光控长延时LED路灯控制器与设计斯密特触发器

- 触发器在数据完整性和安全方面的应用

- 触发器的考核管理信息系统监控模块的设计和实现

- 城市轨道交通综合监控时钟子系统的实现与工程应用

- IEEE1588时钟同步技术在数字化变电站中应用

- HIROSS空调在守时钟房试运行中存在问题及改进

- HIROSS空调在守时钟房运行中存在的问题及改进

- 时钟系统调试检验批质量验收记录

- P89LPC935驱动数码管显示时钟的设计

- 时钟同步在城市轨道交通自动售检票系统中的应用

- 可重复触发单稳态触发器在检测电路中应用

- TCA785移相触发器的三相控整流电源

- EDA技术的单稳态触发器设计与仿真

- 数据选择器和D触发器的多输入时序电路设计

- 无线光通信PPWM码时隙时钟恢复和解调

- 实时时钟芯片X1228的电源控制器设计