mos晶体管转移特性

将MOS晶体管的栅漏连接,因为VGS=VDS,所以,VDS>VGS-VTN, 导通的器件一定工作在饱和区。这时,晶体管的电流-电压特性应遵循饱和区的萨氏方程:

IDS=KN/2•W/L•(VGS-VTN)2(1+λVDS)

即平方律关系。4种MOS晶体管的平方律转移特性如图所示,这样的连接方式在许多设计中被采用。

mos晶体管造价信息

第一个影响阈值电压的因素是作为介质的二氧化硅(栅氧化层)中的电荷Qss以及电荷的性质。这种电荷通常是由多种原因产生的,其中的一部分带正电,一部分带负电,其净电荷的极性显然会对衬底表面产生电荷感应,从而影响反型层的形成,或者是使器件耗尽,或者是阻碍反型层的形成。Qss通常为可动正电荷。

第二个影响阈值电压的因素是衬底的掺杂浓度。从前面的分析可知,要在衬底的上表面产生反型层,必须施加能够将表面耗尽并且形成衬底少数载流子的积累的栅源电压,这个电压的大小与衬底的掺杂浓度有直接的关系。衬底掺杂浓度(QB)越低,多数载流子的浓度也越低,使衬底表面耗尽和反型所需要的电压VGS越小。

所以,衬底掺杂浓度是一个重要的参数,衬底掺杂浓度越低,器件的阈值电压数值将越小,反之则阈值电压值越高。对于一个成熟稳定的工艺和器件基本结构,器件阈值电压的调整,主要通过改变衬底掺杂浓度或衬底表面掺杂浓度进行。衬底表面掺杂浓度的调整是通过离子注入杂质离子进行。

第三个影响阈值电压的因素是由栅氧化层厚度tOX决定的单位面积栅电容的大小。单位面积栅电容越大,电荷数量变化对VGS的变化越敏感,器件的阈值电压则越小。

实际的效应是,栅氧化层的厚度越薄,单位面积栅电容越大,相应的阈值电压数值越低。但因为栅氧化层越薄,氧化层中的场强越大,因此,栅氧化层的厚度受到氧化层击穿电压的限制。选用其他介质材料做栅介质是当前工艺中的一个方向。例如选用氮氧化硅 SiNxOy 替代二氧化硅是一个微电子技术的发展方向。正在研究其它具有高介电常数的材料,称为高k栅绝缘介质。

第四个对器件阈值电压具有重要影响的参数是栅材料与硅衬底的功函数差ΦMS的数值,这和栅材料性质以及衬底的掺杂类型有关,在一定的衬底掺杂条件下,栅极材料类型和栅极掺杂条件都将改变阈值电压。对于以多晶硅为栅极的器件,器件的阈值电压因多晶硅的掺杂类型以及掺杂浓度而发生变化。

可见,在正常条件下,很容易得到增强型PMOS管。为了制得增强型NMOS管,则需注意减少Qss、Qox,增加QB。采用硅栅工艺对制做增强型NMOS管和绝对值小的增强型PMOS管有利。

mos晶体管阈值电压

MOS管的阈值电压等于backgate和source接在一起时形成channel需要的gate对source偏置电压。如果gate对source偏置电压小于阈值电压,就没有channel。一个特定的晶体管的阈值电压和很多因素有关,包括backgate的掺杂,电介质的厚度,gate材质和电介质中的过剩电荷。每个因素都会被简单的介绍下。

Bakegate的掺杂是决定阈值电压的主要因素。如果backgate越重掺杂,它就越难反转。要反转就要更强的电场,阈值电压就上升了。MOS管的backgate掺杂能通过在gate dielectric表面下的稍微的implant来调整。这种implant被叫做阈值调整implant(或Vt调整implant)。

考虑一下Vt调整implant对NMOS管的影响。如果implant是由acceptors组成的,那么硅表面就更难反转,阈值电压也升高了。如果implant是由donors组成的,那么硅表面更容易反转,阈值电压下降。如果注入的donors够多,硅表面实际上就反向掺杂了。这样,在零偏置下就有了一薄层N型硅来形成永久的channel。随着GATE偏置电压的上升,channel变得越来越强的反转。随着GATE偏置电压的下降,channel变的越来越弱,最后消失了。这种NMOS管的阈值电压实际上是负的。这样的晶体管称为耗尽模式NMOS,或简单的叫做耗尽型NMOS。相反,一个有正阈值电压的的NMOS叫做增强模式NMOS,或增强型NMOS。绝大多数商业化生产的MOS管是增强型器件,但也有一些应用场合需要耗尽型器件。耗尽型PMOS也能被生产出来。这样的器件的阈值电压是正的。

耗尽型的器件应该尽量的被明确的标识出来。不能靠阈值电压的正负符号来判断,因为通常许多工程师忽略阈值电压的极性。因此,应该说“阈值电压为0.7V的耗尽型PMOS”而不是阈值电压为0.7V的PMOS。很多工程师会把后者解释为阈值电压为-0.7V的增强型PMOS而不是阈值电压为+0.7V的耗尽型PMOS。明白无误的指出是耗尽型器件可以省掉很多误会的可能性。

为了区别不同的MOS管有很多特殊的符号。图7就是这些符 号。(符号A,B,E,F,G,和H被许多不同的作者使用)符号A和B分别是NMOS和PMOS管的标准符号。这些符号在工业界没有被普遍使用;相反,符号C和D分别代表NMOS和PMOS。这些符号被设计的很像NPN和PNP管。这么做能突出MOS和双极型电路之间基本的相似点。符号E和F用在backgates接到已知电位上时。每个MOS管都有一个backgate,所以它总得接到什么地方。符号E和F可能有点让人看不懂,因为读者必须自己推断bakgate的接法。尽管如此,这些符号还是非常流行,因为他们使电路同看上去更易读。符号G和H经常被用在耗尽型器件上,符号中从drain到source的粗线就表示了零偏置时的channel。符号I和J表示高电位drain的非对称晶体管,符号K和L表示drain和source都是高电位的对称晶体管。除了这些,MOS管还有其他很多电路符号;图1.24仅仅是其中的一小部分。

电介质在决定阈值电压方面也起了重要作用。厚电介质由于比较厚而削弱了电场。所以厚电介质使阈值电压上升,而薄电介质使阈值电压下降。理论上,电介质成分也会影响电场强度。而实际上,几乎所有的MOS管都用纯二氧化硅作为gate dielectric。这种物质可以以极纯的纯度和均匀性生长成非常薄的薄膜;其他物质跟它都不能相提并论。因此其他电介质物质只有很少的应用。(也有用高介电常数的物质比如氮化硅作为gate dielectric的器件。有些作者把所有的MOS类晶体管,包括非氧化物电介质,称为insulated-gate field effect transistor(IGFET))

gate的物质成分对阈值电压也有所影响。如上所述,当GATE和BACKGATE短接时,电场就出现在gate oxide上。这主要是因为GATE和BACKGATE物质之间的work function差值造成的。大多数实际应用的晶体管都用重掺杂的多晶硅作为gate极。改变多晶硅的掺杂程度就能控制它的work function。

GATE OXIDE或氧化物和硅表面之间界面上过剩的电荷也可能影响阈值电压。这些电荷中可能有离子化的杂质原子,捕获的载流子,或结构缺陷。电介质或它表面捕获的电荷会影响电场并进一步影响阈值电压。如果被捕获的电子随着时间,温度或偏置电压而变化,那么阈值电压也会跟着变化。

mos晶体管转移特性常见问题

-

首先根据你的需求决定选择NPN还是PNP(建议尽量选用NPN,应为同工艺的NPN管子要比PNP的相对便宜、性能相对优越)然后根据你的电路环境决定管子耐压Vds,过流Id,根据导通损耗需求选择导通电阻R...

-

晶体管(transistor)是一种固体半导体器件,可以用于检波、整流、放大、开关、稳压、信号调制和许多其它功能。晶体管作为一种可变开关,基于输入的电压,控制流出的电流,开关速度可以非常之快,在实验室...

-

只用一种载流子进行导电的晶体管称为单极型晶体管。

MOS晶体管的跨导gm表示交流小信号时衡量MOS器件VGS对IDS的控制能力(VDS恒定)的参数,也是MOS晶体管的一个极为重要的参数。 (忽略沟道长度调制效应,λ=0,在以下分析中,如未出现λ参数,均表示λ=0的情况)。

MOS晶体管的最高工作频率被定义为:当对栅极输入电容CGC的充放电电流和漏源交流电流的数值相等时,所对应的工作频率为MOS晶体管的最高工作频率。这是因为当栅源间输入交流信号时,由源极增加(减少)流入的电子流,一部分通过沟道对电容充(放)电,一部分经过沟道流向漏极,形成漏源电流的增量。因此,当变化的电流全部用于对沟道电容充放电时,晶体管也就失去了放大能力。

mos晶体管开通过程

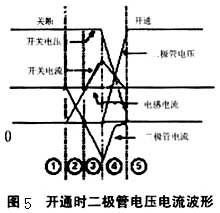

开关管的开关模式电路如图4所示,二极管可是外接的或MOS管固 有的。开关管在开通时的二极管电压、电流波形如图5所示。在图5的阶段1开关管关断,开关电流为零,此时二极管电流和电感电流相等;在阶段2开关导通,开关电流上升,同时二极管电流下降。开关电流上升的斜率和二极管电流下降的斜率的绝对值相同,符号相反;在阶段3开关电流继续上升,二极管电流继续下降,并且二极管电流符号改变,由正转到负;在阶段4,二极管从负的反向最大电流IRRM开始减小,它们斜率的绝对值相等;在阶段5开关管完全开通,二极管的反向恢复完成,开关管电流等于电感电流。

MOS晶体管

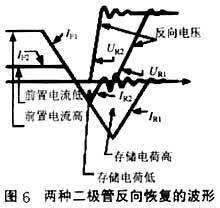

图6是存储电荷高或低的两种二极管电流、电压波形。从图中可以看出存储电荷少时,反向电压的斜率大,并且会产生有害的振动。而前置电流低则存储电荷少,即在空载或轻载时是最坏条件。所 以进行优化驱动电路设计时应着重考虑前置电流低的情况,即空载或轻载的情况,应使这时二极管产生的振动在可接受范围内。

mos晶体管工作特点

栅极控制器件,源、漏扩散区为反偏pn结,外加电压,器件不导通,处于隔离状态;外加栅极电压,直到电压达到一个阈值(称为阈值电压VT),器件导通。

以SiO2为栅介质时,叫MOS器件,这是最常使用的器件形式。历史上也出现过以Al2O3为栅介质的MAS器件和以 Si3N4为栅介质的MNS器件,以及以SiO2+Si3N4为栅介质的MNOS器件,统称为金属-绝缘栅-半导体器件--MIS 器件。

以Al为栅电极时,称铝栅器件。以重掺杂多晶硅(Poly-Si) 为栅电极时, 称硅栅器件。它是当前MOS器件的主流器件。 硅栅工艺是利用重掺杂的多晶硅来代替铝做为MOS管的栅电极,使MOS电路特性得到很大改善,它使|VTP|下降 1.1V,也容易获得合适的VTN值并能提高开关速度和集成度。

硅栅工艺具有自对准作用,这是由于硅具有耐高温的性质。栅电极,更确切的说是在栅电极下面的介质层,是限定源、漏扩散区边界的扩散掩膜,使栅区与源、漏交迭的密勒电容大大减小,也使其它寄生电容减小,使器件的频率特性得到提高。另外,在源、漏扩散之前进行栅氧化,也意味着可得到浅结。

铝栅工艺为了保证栅金属与漏极铝引线之间有一定的间隔,要求漏扩散区面积要大些。而在硅栅工艺中覆盖源漏极的铝引线可重迭到栅区,这是因为有一绝缘层将栅区与源漏电极引线隔开,从而可使结面积减少30%~40%。

硅栅工艺还可提高集成度,这不仅是因为扩散自对准作用可使单元面积大为缩小,而且因为硅栅工艺可以使用“二层半布线”即一层铝布线,一层重掺杂多晶硅布线,一层重掺杂的扩散层布线。由于在制作扩散层时,多晶硅要起掩膜作用,所以扩散层不能与多晶硅层交叉,故称为两层半布线.铝栅工艺只有两层布线:一层铝布线,一层扩散层布线。硅栅工艺由于有两层半布线,既可使芯片面积比铝栅缩小50%又可增加布线灵活性。

当然,硅栅工艺较之铝栅工艺复杂得多,需增加多晶硅淀积、等离子刻蚀工序,而且由于表面层次多,台阶比较高,表面断铝,增加了光刻的困难,所以又发展了以Si3N4作掩膜的局部氧化LOCOS--Local oxidation on silicon (又称为 MOSIC 的局部氧化隔离工艺Local Oxidation Isolation for MOSIC) ,或称等平面硅栅工艺。

扩散条连线由于其电容较大,漏电流也较大,所以尽量少用,一般是将相应管子的源或漏区加以延伸而成。扩散条也用于短连线,注意扩散条不能跨越多晶硅层,有时把这层连线称为“半层布线”。因硼扩散薄层电阻为30~120Ω/□,比磷扩散的R□大得多,所以硼扩散连线引入的分布电阻更为可观,扩散连线的寄生电阻将影响输出电平是否合乎规范值,同时也因加大了充放电的串联电阻而使工作速度下降。因此,在CMOS电路中,当使用硼扩散条做连线用时要考虑到这一点。

当在NMOS的栅上施加相对于源的正电压VGS时,栅上的正电荷在P型衬底上感应出等量的负电荷,随着VGS的增加,衬底中接近硅-二氧化硅界面的表面处的负电荷也越多。其变化过程如下:当VGS比较小时,栅上的正电荷还不能使硅-二氧化硅界面处积累可运动的电子电荷,这是因为衬底是P型的半导体材料,其中的多数载流子是正电荷空穴,栅上的正电荷首先是驱赶表面的空穴,使表面正电荷耗尽,形成带固定负电荷的耗尽层。

这时,虽然有VDS的存在,但因为没有可运动的电子,所以,并没有明显的源漏电流出现。增加VGS,耗尽层向衬底下部延伸,并有少量的电子被吸引到表面,形成可运动的电子电荷,随着VGS的增加,表面积累的可运动电子数量越来越多。这时的衬底负电荷由两部分组成:表面的电子电荷与耗尽层中的固定负电荷。如果不考虑二氧化硅层中的电荷影响,这两部分负电荷的数量之和等于栅上的正电荷的数量。当电子积累达到一定水平时,表面处的半导体中的多数载流子变成了电子,即相对于原来的P型半导体,具有了N型半导体的导电性质,这种情况称为表面反型。

根据晶体管理论,当NMOS晶体管表面达到强反型时所对应的VGS值,称为NMOS晶体管的阈值电压VTN (Threshold voltage for N-channel transistor)。这时,器件的结构发生了变化,自左向右,从原先的 n+-p-n+结构,变成了n+-n-n+结构,表面反型的区域被称为沟道区。在VDS的作用下,N型源区的电子经过沟道区到达漏区,形成由漏流向源的漏源电流。显然,VGS的数值越大,表面处的电子密度越大,相对的沟道电阻越小,在同样的VDS的作用下,漏源电流越大。

当VGS大于VTN,且一定时,随着VDS的增加,NMOS的沟道区的形状将逐渐的发生变化。在VDS较小时,沟道区基本上是一个平行于表面的矩形,当VDS增大后,相对于源端的电压VGS和VDS在漏端的差值VGD逐渐减小,并且因此导致漏端的沟道区变薄,当达到VDS=VGS-VTN时,在漏端形成了VGD=VGS-VDS=VTN的临界状态,这一点被称为沟道夹断点,器件的沟道区变成了楔形,最薄的点位于漏端,而源端仍维持原先的沟道厚度。器件处于VDS=VGS-VTN的工作点被称为临界饱和点。

在逐渐接近临界状态时,随着VDS的增加,电流的变化偏离线性,NMOS晶体管的电流-电压特性发生弯曲。在临界饱和点之前的工作区域称为非饱和区,显然,线性区是非饱和区中VDS很小时的一段。继续在一定的VGS条件下增加VDS (VDS>VGS-VTN),在漏端的导电沟道消失,只留下耗尽层,沟道夹断点向源端趋近。由于耗尽层电阻远大于沟道电阻,所以这种向源端的趋近实际上位移值∆L很小,漏源电压中大于VGS-VTN的部分落在很小的一段由耗尽层构成的区域上,有效沟道区内的电阻基本上维持临界时的数值。因此,再增加源漏电压VDS,电流几乎不增加,而是趋于饱和。这时的工作区称为饱和区。NMOS晶体管的电流—电压特性曲线如图3所示。

事实上,由于∆L的存在,实际的沟道长度L将变短,对于L比较大的 器件,∆L/L比较小,对器件的性能影响不大,但是,对于短沟道器件,这个比值将变大,对器件的特性产生影响。器件的电流-电压特性在饱和区将不再是水平直线的性状,而是向上倾斜,也就是说,工作在饱和区的NMOS器件的电流将随着VDS的增加而增加。这种在VDS作用下沟道长度的变化引起饱和区输出电流变化的效应,被称为沟道长度调制效应。衡量沟道长度调制的大小可以用厄莱(Early)电压VA表示,它反映了饱和区输出电流曲线上翘的程度。

双极性晶体管的输出特性曲线形状与MOS器件的输出特性曲线相似,但线性区与饱和区恰好相反。MOS器件的输出特性曲线的参变量是VGS ,双极性晶体管的输出特性曲线的参变量是基极电流IB。衡量沟道长度调制的大小可以用厄莱(Early)电压VA表示,它反映了饱和区输出电流曲线上翘的程度。

PMOS的工作原理与NMOS相类似。因为PMOS是N型硅衬底,其中的多数载流子是电子,少数载流子是空穴,源漏区的掺杂类型是P型,所以,PMOS的工作条件是在栅上相对于源极施加负电压,亦即在PMOS的栅上施加的是负电荷电子,而在衬底感应的是可运动的正电荷空穴和带固定正电荷的耗尽层,不考虑二氧化硅中存在的电荷的影响,衬底中感应的正电荷数量就等于PMOS栅上的负电荷的数量。当达到强反型时,在相对于源端为负的漏源电压的作用下,源端的正电荷空穴经过导通的P型沟道到达漏端,形成从源到漏的源漏电流。同样地,VGS越负(绝对值越大),沟道的导通电阻越小,电流的数值越大。

NMOS一样,导通的PMOS的工作区域也分为非饱和区,临界饱和点和饱和区。当然,不论NMOS还是PMOS,当未形成反型沟道时,都处于截止区,其电压条件是:

VGSVTP (PMOS),

值得注意的是,PMOS的VGS和VTP都是负值。

以上的讨论,都有一个前提条件,即当VGS=0时没有导电沟道,只有当施加在栅上的电压绝对值大于器件的阈值电压的绝对值时,器件才开始导通,在漏源电压的作用下,才能形成漏源电流。以这种方式工作的MOS器件被称为增强型(enhancement mode),又称常关闭型(normally-off) MOS晶体管。所以,上面介绍的是增强型NMOS晶体管和增强型PMOS晶体管。

除了增强型MOS器件外,还有一类MOS器件,它们在栅上的电压值为零时(VGS=0),在衬底上表面就已经形成了导电沟道,在VDS的作用下就能形成漏源电流。这类MOS器件被称为耗尽型(depletion mode),又称常开启型(normally-on) MOS晶体管。

耗尽型MOS晶体管分为耗尽型NMOS晶体管和耗尽型PMOS晶体管。对于耗尽型器件,由于VGS=0时就存在导电沟道,因此,要关闭沟道将施加相对于同种沟道增强型MOS管的反极性电压。对耗尽型NMOS晶体管,由于在VGS=0时器件的表面已经积累了较多的电子,因此,必须在栅极上施加负电压,才能将表面的电子“赶走”。同样地,对耗尽型PMOS晶体管,由于在VGS=0时器件的表面已经存在积累的正电荷空穴,因此,必须在栅极上施加正电压,才能使表面导电沟道消失。

使耗尽型器件的表面沟道消失所必须施加的电压,称为夹断电压 VP (pinch-off),显然,NMOS的夹断电压VPN0。耗尽型NMOS晶体管夹断电压VP的符号为负。增强型NMOS晶体管阈值电压VT的符号为正。

耗尽型器件的初始导电沟道的形成主要来自两个方面:①栅与衬底之间的二氧化硅介质中含有的固定电荷的感应;②通过工艺的方法在器件衬底的表面形成一层反型材料。显然,前者较后者具有不确定性,二氧化硅中的固定正电荷是在二氧化硅形成工艺中或后期加工中引入的,通常是不希望存在的。后者则是为了获得耗尽型MOS晶体管而专门进行的工艺加工,通常采用离子注入的方式在器件的表面形成与衬底掺杂类型相反(与源漏掺杂类型相同)的区域,例如,为获得耗尽型NMOS管,在P型衬底表面通过离子注入方式注入Ⅴ价元素磷或砷,形成N型的掺杂区作为沟道。由于离子注入可以精确的控制掺杂浓度,因此器件的夹断电压值具有可控性。

综上所述,MOS晶体管具有四种基本类型:增强型NMOS晶体管,耗尽型NMOS晶体管,增强型PMOS晶体管,耗尽型PMOS晶体管。在实际的逻辑电路应用中,一般不使用耗尽型PMOS晶体管。

MOS管的等效电路模型及寄生参数如图2所示。图2中各部分的物理意义为:

(1)LG和RG代表封装端到实际的栅极线路的电感和电阻。

(2)C1代表从栅极到源端N+间的电容,它的值是由结构所固定的。

(3)C2+C4代表从栅极到源极P区间的电容。C2是电介质电容,共值是固定的。而C4是由源极到漏极的耗尽区的大小决定,并随栅极电压的大小而改变。当栅极电压从0升到开启电压UGS(th)时,C4使整个栅源电容增加10%~15%。

(4)C3+C5是由一个固定大小的电介质电容和一个可变电容构成,当漏极电压改变极性时,其可变电容值变得相当大。

(5)C6是随漏极电压变换的漏源电容。

MOS管输入电容(Ciss)、跨接电容(CRSS)、输出电容(Coss)和栅源电容、栅漏电容、漏源电容间的关系如下:

MOSFET的结构

MOSFET是Metal-Oxide-Silicon Field Effect Transistor的英文缩写,平面型器件结构,按照导电沟道的不同可以分为NMOS和PMOS器件。MOS器件基于表面感应的原理,是利用垂直的栅压VGS实现对水平IDS的控制。它是多子(多数载流子)器件。用跨导描述其放大能力。MOSFET晶体管的截面图如图1所示在图中,S=Source,G=Gate,D=Drain。

NMOS和PMOS在结构上完全相像,所不同的是衬底和源漏的掺杂类型。简单地说,NMOS是在P型硅的衬底上,通过选择掺杂形成N型的掺杂区,作为NMOS的源漏区;PMOS是在N型硅的衬底上,通过选择掺杂形成P型的掺杂区,作为PMOS的源漏区。如图所示,两块源漏掺杂区之间的距离称为沟道长度L,而垂直于沟道长度的有效源漏区尺寸称为沟道宽度W。对于这种简单的结构,器件源漏是完全对称的,只有在应用中根据源漏电流的流向才能最后确认具体的源和漏。

器件的栅电极是具有一定电阻率的多晶硅材料,这也是硅栅MOS器件的命名根据。在多晶硅栅与衬底之间是一层很薄的优质二氧化硅,它是绝缘介质,用于绝缘两个导电层:多晶硅栅和硅衬底,从结构上看,多晶硅栅-二氧化硅介质-掺杂硅衬底(Poly-Si--SiO2--Si)形成了一个典型的平板电容器,通过对栅电极施加一定极性的电荷,就必然地在硅衬底上感应等量的异种电荷。这样的平板电容器的电荷作用方式正是MOS器件工作的基础。

mos晶体管简介

MOS晶体管金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。MOS管构成的集成电路称为MOS集成电路,而PMOS管和NMOS管共同构成的互补型MOS集成电路即为CMOS-IC。

金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。MOS管构成的集成电路称为MOS集成电路,而PMOS管和NMOS管共同构 成的互补型MOS集成电路即为CMOS-IC

在实际工作中,经常出现衬底和源极不相连的情况,此时,VBS不等于0。由基本的pn结理论可知,处于反偏的pn结的耗尽层将展宽。上图说明了NMOS管在VDS较小时的衬底耗尽层变化情况,图中的浅色边界是衬底偏置为0时的耗尽层边界。当衬底与源处于反偏时,衬底中的耗尽区变厚,使得耗尽层中的固定电荷数增加。由于栅电容两边电荷守衡,所以,在栅上电荷没有改变的情况下,耗尽层电荷的增加,必然导致沟道中可动电荷的减少,从而导致导电水平下降。若要维持原有的导电水平,必须增加栅压,即增加栅上的电荷数。对器件而言,衬底偏置电压的存在,将使MOS晶体管的阈值电压的数值提高。对NMOS,VTN更正,对PMOS,VTP更负,即阈值电压的绝对值提高了。

γ为衬底偏置效应系数,它随衬底掺杂浓度而变化,典型值:NMOS晶体管,γ=0.7~3.0。PMOS晶体管,γ=0.5~0.7对于PMOS晶体管,∆VT取负值,对NMOS晶体管,取正值。

对处于动态工作的器件而言,当衬底接一固定电位时,衬偏电压将随着源节点电位的变化而变化,产生对器件沟道电流的调制,这称为背栅调制,用背栅跨导gmB来定义这种调制作用的大小:

其中三个重要端口参数:gm、gds和gmb对应了MOS器件的三个信号端口G-S、D-S、B-S,它们反映了端口信号对漏源电流的控制作用。

mos晶体管转移特性文献

社保转移证明

社保转移证明

证 明 信《范本一》 中山市社保局: 兹有我公司员工 ,身份证号码: , 籍贯: ;该员工已于 年 月 日办好离职离厂 手续并结束劳动关系,现申请办理基本养老保险关系转移接续手续,请贵局 给予办理。 特此证明 有限公司 年 月 日 证 明 信 中山市社保局: 兹有我公司员工 ,身份证号码: , 籍贯: ;该员工已于 年 月 日办好离职离厂手 续并结束劳动关系,现申请办理基本养老保险关系转移接续手续,请贵局给 予办理。 特此证明 有限公司 年 月 日 证 明《范本二》 中山市社保局: 兹有我公司( 有限公司)员工 身份 证号码: ,因申请于 年 月 日辞 职返乡,现需办理社会保险 关系转移接续手续 ,请中山市社会保险局给 予办理为谢 ! 特此证明 有限公司 2015 年 月 日 证 明 信 中山市社保局: 兹有我公司员工 ,身

第五章双极型晶体管开关特性

第五章双极型晶体管开关特性

第五章双极型晶体管开关特性

改变栅压可以改变沟道中的电子密度,从而改变沟道的电阻。这种MOS场效应晶体管称为P沟道增强型场效应晶体管。如果N型硅衬底表面不加栅压就已存在P型反型层沟道,加上适当的偏压,可使沟道的电阻增大或减小。这样的MOS场效应晶体管称为P沟道耗尽型场效应晶体管。统称为PMOS晶体管。

P沟道MOS晶体管的空穴迁移率低,因而在MOS晶体管的几何尺寸和工作电压绝对值相等的情况下,PMOS晶体管的跨导小于N沟道MOS晶体管。此外,P沟道MOS晶体管阈值电压的绝对值一般偏高,要求有较高的工作电压。它的供电电源的电压大小和极性,与双极型晶体管——晶体管逻辑电路不兼容。PMOS因逻辑摆幅大,充电放电过程长,加之器件跨导小,所以工作速度更低,在NMOS电路(见N沟道金属—氧化物—半导体集成电路)出现之后,多数已为NMOS电路所取代。只是,因PMOS电路工艺简单,价格便宜,有些中规模和小规模数字控制电路仍采用PMOS电路技术。

PMOS集成电路是一种适合在低速、低频领域内应用的器件。PMOS集成电路采用-24V电压供电。如图1所示的CMOS-PMOS接口电路采用两种电源供电。采用直接接口方式,一般CMOS的电源电压选择在10~12V就能满足PMOS对输入电平的要求。

MOS场效应晶体管具有很高的输入阻抗,在电路中便于直接耦合,容易制成规模大的集成电路。

金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。由MOS管构成的集成电路称为MOS集成电路,而由PMOS管和NMOS管共同构成的互补型MOS集成电路即为 CMOS-IC( Complementary MOS Integrated Circuit)。

目前使用最最广泛的晶体管是CMOS晶体管,CMOS晶体管特点是什么?首先CMOS晶体管功耗和抗干扰能力优于同时期的TTL器件,而且速度和TTL器件相当,所以CMOS取代TTL是大势所趋,我们看到目前集成电路上的晶体管还有几乎所有PLD器件都是采用CMOS技术,这一点就说明了CMOS的大行其道。

N沟MOS晶体管简介

金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。MOS管构 成的集成电路称为MOS集成电路,而PMOS管和NMOS管共同构成的互补型MOS集成电路即为CMOS-IC。

由p型衬底和两个高浓度n扩散区构成的MOS管叫作n沟道MOS管,该管导通时在两个高浓度n扩散区间形成n型导电沟道。n沟道增强型MOS管必须在栅极上施加正向偏压,且只有栅源电压大于阈值电压时才有导电沟道产生的n沟道MOS管。n沟道耗尽型MOS管是指在不加栅压(栅源电压为零)时,就有导电沟道产生的n沟道MOS管。

NMOS集成电路是N沟道MOS电路,NMOS集成电路的输入阻抗很高,基本上不需要吸收电流,因此,CMOS与NMOS集成电路连接时不必考虑电流的负载问题。NMOS集成电路大多采用单组正电源供电,并且以5V为多。CMOS集成电路只要选用与NMOS集成电路相同的电源,就可与NMOS集成电路直接连接。不过,从NMOS到CMOS直接连接时,由于NMOS输出的高电平低于CMOS集成电路的输入高电平,因而需要使用一个(电位)上拉电阻R,R的取值一般选用2~100KΩ。

- 相关百科

- 相关知识

- 相关专栏

- 稳压管

- 双壁热缩管

- 晶体管毫伏表

- 散热片加热管

- 信息型光源

- 桃花心木亚科

- 带阻三极管

- 陶瓷电加热管

- 双转子锤式超细破碎机

- 玻璃放电管

- N沟MOS晶体管

- 碱性氮测定仪

- 304不锈钢焊接管

- 单头加热管

- 金叶黄槐

- 彩色电工管

- 杂散电容对交流法微电容测量电路噪声特性影响的分析

- 以空气为携热介质的开式太阳能蓄能热泵循环特性

- 新的水泵水轮机全特性曲线处理方法及其工程应用

- 应用于机电暂态仿真的直流输电系统控制特性算法

- 用于电力电缆中间接头的硅橡胶材料吸水特性分析

- 双螺杆真空泵转子的接触线及动平衡特性

- 关于印发工程设计文件质量特性和质量评定一指南通知

- 工频零点电流转移限流及405kV快速真空开关仿真

- 工程用水泥基复合材料(ECC)进展与工程特性

- 公路隧道施工锚杆支护应力特性及长度选择有限元分析

- 公路钢护栏圆形立柱与土壤基础相互作用力学特性

- 基于AMESim螺纹插装式平衡阀动态特性仿真

- 基于AMESim液压起重机负载敏感平衡阀特性仿真

- 基于MATLAB超高压电磁换向球阀动态特性

- 夯实水泥土桩复合地基动力特性和时程响应影响因素分析

- 国内,外大中型水利水电工程特性检索系统设计和开发