漏极

漏极基本信息

| 中文名 | 漏极 | 外文名 | drain |

|---|---|---|---|

| 晶体管 | 是由两种极性的载流子 | 易于集成 | 没有二次击穿现象 |

| 夹着一层 | 低掺杂的N区(N区一般做得很薄) | ||

一般的晶体管是由两种极性的载流子,即多数载流子和反极性的少数载流子参与导电,因此称为双极型晶体管,而FET仅是由多数载流子参与导电,它与双极型相反,也称为单极型晶体管。它属于电压控制型半导体器件,具有输入电阻高(108~109Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者。

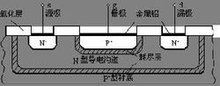

在两个高掺杂的P区中间,夹着一层低掺杂的N区(N区一般做得很薄),形成了两个PN结。在N区的两端各做一个欧姆接触电极,在两个P区上也做上欧姆电极,并把这两P区连起来,就构成了一个场效应管 。

漏极造价信息

1.利用外部电路的驱动能力,减少IC内部的驱动, 或驱动比芯片电源电压高的负载。

2.可以将多个开漏输出的Pin,连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。这也是I2C,SMBus等总线判断总线占用状态的原理。

3.由于漏级开路,所以后级电路必须接一上拉电阻,上拉电阻的电源电压就可以决定输出电平。这样就可以进行任意电平的转换了。

4.源极开路提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出 。2100433B

漏极概述

一般的晶体管是由两种极性的载流子,即多数载流子和反极性的少数载流子参与导电,因此称为双极型晶体管,而FET仅是由多数载流子参与导电,它与双极型相反,也称为单极型晶体管。它属于电压控制型半导体器件,具有输入电阻高(10^8~10^9Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者

在两个高掺杂的P区中间,夹着一层低掺杂的N区(N区一般做得很薄),形成了两个PN结。在N区的两端各做一个欧姆接触电极,在两个P区上也做上欧姆电极,并把这两P区连起来,就构成了一个场效应管。

N型导电沟道结型场效应管的电路符号。

将两个P区的引出线连在一起作为一个电极,称为栅极,在N型硅片两端各引出一个电极,分别称为源极和漏极,很薄的N区称为导电沟道。共漏极放大电路--源极输出器

栅极简称为G ,源极简称为S,漏极简称为D。

漏极常见问题

-

在开关电源中,通常的设计会在MOS管的漏极或者IGBT的C如你所说的加电阻并二极管(应该还要串一电容)至电源的正极。此电路是缓冲电路,吸收电路尖峰,避免开关过程中产生的高压尖峰击穿开关管导致损坏。在不...

-

一般TT、TN-C系统采用漏电保护器,漏电空开我没见过单匹的(只断开相线),之所以要断开零线,是怕设备漏电后,沿着零线传输到其他设备外壳去,防止漏电范围扩大

-

根据品牌价格大概60~300之间不等。四极漏电保护器的正确使用应建立在弄清漏电保护器本身的结构,即N线是否穿过零序电流互感器与负载类型,即负载是否对中性线有要求的基础上。笔者以为,三极漏电保护器应定义...

将两个P区的引出线连在一起作为一个电极,称为栅极,在N型硅片两端各引出一个电极,分别称为源极和漏极,很薄的N区称为导电沟道。共漏极放大电路——源极输出器。

栅极简称为G,源极简称为S,漏极简称为D 。

漏极文献

共漏极双功率MOSFET封装研究

共漏极双功率MOSFET封装研究

针对适用于锂电池保护电路特点要求的共漏极功率MOSFET的封装结构进行了研发和展望。从传统的TSSOP-8发展到替代改进型SOT-26,一直到芯片级尺寸的微型封装外形,其封装效率越来越高,接近100%。同时,在微互连和封装结构的改进方面,逐渐向短引线或焊球无引线、平坦式引脚、超薄型封装和漏极焊盘散热片暴露的方向发展,增强了封装的电性能和热性能。

三极与四极漏电保护器的简单分析

三极与四极漏电保护器的简单分析

三极与四极漏电保护器的简单分析 三极与四极漏电保护器的简单分析 低压配电系统中装设漏电保护器是防止人身触电的有效措 施,也可以防止因漏电而引发的电气火灾及设备损坏事故。 漏电保护器一般分为一极、二极、三极、四极。其中一极、 二极漏电保护器的结构原理图,它们的主要区别在于当漏电 事故发生时是否断开零线。其工作原理均为通过检测相线、 零线电流的相量和是否为零来判定是否有漏电事故发生。讨 论的重点是三极、四极漏电保护器的工作原理与应用场合的 差异。 我查阅一些厂家提供的三、四极漏电保护器结构原理图时 发现一些问题,源自某国产品牌开关制造商产品资料,源自 某进口品牌开关制造商产品资料。我们发现二者的四极漏电 保护器的结构原理图并无区别,但三极漏电保护的结构原理 图却存在重大不同,并由此引发其使用也有重大区别。 在分析之前,需要明确一个概念,即“负载三相平衡”。 在三相交流电系统中,负载三相平衡时,

开漏极就是漏极开路,漏极开路是驱动电路的输出三极管的集电极开路,可以通过外接的上拉电阻提高驱动能力。

特点

组成开漏形式的电路有以下几个特点

1. 利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很小的栅极驱动电流。

2. 可以将多个开漏输出的Pin,连接到一条线上。形成“与逻辑”关系。当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。

3. 可以利用改变上拉电源的电压,改变传输电平。IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。

4. 开漏Pin不连接外部的上拉电阻,则只能输出低电平。

5. 标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。2100433B

除跨导Gfs、开启电压UT以及td(on)、tr、td(off)和tf之外还有:

(1)漏极电压UDS——电力MOSFET电压定额

(2)漏极直流电流ID和漏极脉冲电流幅值IDM——电力MOSFET电流定额

(3)栅源电压UGS—— UGS>20V将导致绝缘层击穿 。

(4)极间电容——极间电容CGS、CGD和CDS

间加正向电压使N型半导体中的多数载流子-电子由源极出发,经过沟道到达漏极形成漏极电流ID。

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压大于参数手册中给定的Vgs就可以了,漏极D接电源,源极S接地。需要注意的是Vgs指的是栅极G与源极S的压差,所以当NMOS作为高端驱动时候,当漏极D与源极S导通时,漏极D与源极S电势相等,那么栅极G必须高于源极S与漏极D电压,漏极D与源极S才能继续导通。2100433B

- 相关百科

- 相关知识

- 相关专栏

- BAD808-G LED防爆投光灯

- 壁式采煤法

- 睡莲生态城

- 多孔砖机

- 绵毛叶脉睡莲

- 倾斜分层走向长壁下行垮落采煤法

- 全自动砌块成型机

- 四壁落地房

- 瓦板房

- 液压制砖机

- 拉祜族民居

- 高湿物料粉碎机

- ULN2803

- 河溪睡莲

- BGL-G防水防尘防腐不锈钢防爆灯

- 防水防尘防腐全塑灯

- 可关断晶闸管(GTO)直接门极驱动电路

- 整理了一些钢筋对工程量时候容易漏算或者忽视的项目

- 水电站平板式尾水闸门漏水封堵装置与应用

- 增安型2/4极双速高压箱式空-水冷三相异步电动机

- 基于PLC矿用智能低压馈电开关选择性漏电保护系统

- 化学示踪实验技术在水利工程渗漏检测中应用(英文)

- 框架结构新型填充墙体材料渗漏裂纹质量通病防治措施

- 基于LabVIEW窄隙室探测器漏电流自动监测系统

- 埋地钢质管道阴极保护系统附属设施定位检测方法实践

- 云南省节能技术服务中心积极推进循环流化床锅炉技术改造

- 建筑施工现场临时用电漏电保护器检测记录表

- 抗裂防漏专项施工方案

- 正泰电气NV1-24-TP户内固封极柱真空断路器

- 梅林一村八区高层住宅工程工程防渗漏措施措施

- 城市轨道交通地下车站附属结构深基坑围护渗漏风险监理控制

- 带三相四线制二极管整流桥负载的同步发电机的等效电路模型