L2CacheIntel双核心处理器的二级缓存

Intel的双核心CPU主要有Pentium D、Pentium EE、Core Duo三种,其中Pentium D、Pentium EE的二级缓存方式完全相同。Pentium D和Pentium EE的二级缓存都是CPU内部两个内核具有互相独立的二级缓存,其中,8xx系列的Smithfield核心CPU为每核心1MB,而9xx系列的Presler核心CPU为每核心2MB。这种CPU内部的两个内核之间的缓存数据同步是依靠位于主板北桥芯片上的仲裁单元通过前端总线在两个核心之间传输来实现的,所以其数据延迟问题比较严重,性能并不尽如人意。

Core Duo使用的核心为Yonah,它的二级缓存则是两个核心共享2MB的二级缓存,共享式的二级缓存配合Intel的“Smart cache”共享缓存技术,实现了真正意义上的缓存数据同步,大幅度降低了数据延迟,减少了对前端总线的占用,性能表现不错,是双核心处理器上最先进的二级缓存架构。今后Intel的双核心处理器的二级缓存都会采用这种两个内核共享二级缓存的“Smart cache”共享缓存技术。

L2Cache造价信息

CPU在缓存中找到有用的数据被称为命中,当缓存中没有CPU所需的数据时(这时称为未命中),CPU才访问内存。从理论上讲,在一颗拥有二级缓存的CPU中,读取一级缓存的命中率为80%。也就是说CPU一级缓存中找到的有用数据占数据总量的80%,剩下的20%从二级缓存中读取。由于不能准确预测将要执行的数据,读取二级缓存的命中率也在80%左右(从二级缓存读到有用的数据占总数据的16%)。那么还有的数据就不得不从内存调用,但这已经是一个相当小的比例了。较高端的CPU中,还会带有三级缓存,它是为读取二级缓存后未命中的数据设计的—种缓存,在拥有三级缓存的CPU中,只有约5%的数据需要从内存中调用,这进一步提高了CPU的效率。

为了保证CPU访问时有较高的命中率,缓存中的内容应该按一定的算法替换。一种较常用的算法是“最近最少使用算法”(LRU算法),它是将最近一段时间内最少被访问过的行淘汰出局。因此需要为每行设置一个计数器,LRU算法是把命中行的计数器清零,其他各行计数器加1。当需要替换时淘汰行计数器计数值最大的数据行出局。这是一种高效、科学的算法,其计数器清零过程可以把一些频繁调用后再不需要的数据淘汰出缓存,提高缓存的利用率。

CPU产品中,一级缓存的容量基本在4KB到64KB之间,二级缓存的容量则分为128KB、256KB、512KB、1MB、2MB等。一级缓存容量各产品之间相差不大,而二级缓存容量则是提高CPU性能的关键。二级缓存容量的提升是由CPU制造工艺所决定的,容量增大必然导致CPU内部晶体管数的增加,要在有限的CPU面积上集成更大的缓存,对制造工艺的要求也就越高。

双核心CPU的二级缓存比较特殊,和以前的单核心CPU相比,最重要的就是两个内核的缓存所保存的数据要保持一致,否则就会出现错误,为了解决这个问题不同的CPU使用了不同的办法:

最早先的CPU缓存是个整体的,而且容量很低,英特尔公司从Pentium时代开始把缓存进行了分类。当时集成在CPU内核中的缓存已不足以满足CPU的需求,而制造工艺上的限制又不能大幅度提高缓存的容量。因此出现了集成在与CPU同一块电路板上或主板上的缓存,此时就把 CPU内核集成的缓存称为一级缓存,而外部的称为二级缓存。一级缓存中还分数据缓存(Data Cache,D-Cache)和指令缓存(Instruction Cache,I-Cache)。二者分别用来存放数据和执行这些数据的指令,而且两者可以同时被CPU访问,减少了争用Cache所造成的冲突,提高了处理器效能。英特尔公司在推出Pentium 4处理器时,用新增的一种一级追踪缓存替代指令缓存,容量为12KμOps,表示能存储12K条微指令。

随着CPU制造工艺的发展,二级缓存也能轻易的集成在CPU内核中,容量也在逐年提升。再用集成在CPU内部与否来定义一、二级缓存,已不确切。而且随着二级缓存被集成入CPU内核中,以往二级缓存与CPU大差距分频的情况也被改变,此时其以相同于主频的速度工作,可以为CPU提供更高的传输速度。

L2CacheIntel双核心处理器的二级缓存常见问题

-

二级缓存并不是越大越好,假如我们将CPU比作1个工厂,那CPU核心就是生产车间,缓存就是原料和半成品仓库,当生产需时,原料先从近来的一级缓存中寻找,当找不到时再到二级缓存中找。而内存就可能原料产地,直...

-

英特尔处理器分为很多种,比如早一点的奔腾双核,酷睿2 i3 xxx i5 xxi7 &nbs...

-

首先你要知道硬盘缓存的作用:1、预读取,举例来说(不是完全准确的)就是读取硬盘数据的时候,你所需的数据在N簇,会读取硬盘上N-1簇、N簇、N+1簇的数据到缓存中去,如果你在读完N簇数据后需要再读取N+...

当CPU要读取一个数据时,首先从缓存中查找,如果找到就立即读取并送给CPU处理;如果没有找到,就用相对慢的速度从内存中读取并送给CPU处理,同时把这个数据所在的数据块调入缓存中,可以使得以后对整块数据的读取都从缓存中进行,不必再调用内存。

正是这样的读取机制使CPU读取缓存的命中率非常高(大多数CPU可达90%左右),也就是说CPU下一次要读取的数据90%都在缓存中,只有大约10%需要从内存读取。这大大节省了CPU直接读取内存的时间,也使CPU读取数据时基本无需等待。总的来说,CPU读取数据的顺序是先缓存后内存。

CPU缓存(Cache Memory)位于CPU与内存之间的临时存储器,它的容量比内存小但交换速度快。在缓存中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可避开内存直接从缓存中调用,从而加快读取速度。由此可见,在CPU中加入缓存是一种高效的解决方案,这样整个内存储器(缓存 内存)就变成了既有缓存的高速度,又有内存的大容量的存储系统了。缓存对CPU的性能影响很大,主要是因为CPU的数据交换顺序和CPU与缓存间的带宽引起的。

L1和L2都是计算机中缓存(cache memory)的等级。如果计算机的处理器可以在缓存中找到他下个运算所需的数据,它将省去了到随机存储器(RAM)中寻找这个数据的时间。L1是一级缓存,通常内建于微处理芯片(Chip)中。比如,IntelMMX微处理器(microprocessor)本身是带有一个有32Kb的一级缓存。

L2(就是二级)缓存是在独立芯片(有可能是在一个扩展卡上),它的访问速度能比大的主存要快得多。通常一个二级缓存的大小为1024Kb(1Mb)。

Athlon 64 X2 CPU的核心主要有Manchester和Toledo两种,他们的二级缓存都是CPU内部两个内核具有互相独立的二级缓存,其中,Manchester核心为每核心512KB,而Toledo核心为每核心1MB。处理器内部的两个内核之间的缓存数据同步是依靠CPU内置的System Request Interface(系统请求接口,SRI)控制,传输在CPU内部即可实现。这样一来,不但CPU资源占用很小,而且不必占用内存总线资源,数据延迟也比Intel的Smithfield核心和Presler核心大为减少,协作效率明显胜过这两种核心。不过,由于这种方式仍然是两个内核的缓存相互独立,从架构上来看也明显不如以Yonah核心为代表的Intel的共享缓存技术Smart Cache。2100433B

L2CacheIntel双核心处理器的二级缓存文献

流水线处理器中Cache模块的设计

流水线处理器中Cache模块的设计

流水线结构能大幅提高指令执行速度,但是由于主存读取速度过慢,系统性能的提升仍然受到限制。现实现的Cache设计,是流水线与主存间的高速缓冲器,它能有效地解决访存的瓶颈问题,使流水线功能得到充分发挥。文章首先分析流水线的结构特点,确定Cache的结构功能,在此基础上提出一个组相联映射Cache的设计。分析Cache实现读写操作的具体控制过程,并给出LRU(least recently used)替换算法的实现。最后通过介绍猝发取指操作着重讨论了Cache与流水线间的配合机制。

局域网双核心设计

局域网双核心设计

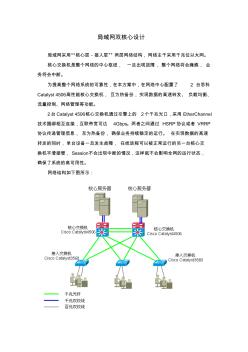

局域网双核心设计 局域网采用“核心层-接入层” 两层网络结构,网络主干采用千兆位以太网。 核心交换机是整个网络的中心枢纽, 一旦出现故障, 整个网络将会瘫痪, 业 务将会中断。 为提高整个网络系统的可靠性,在本方案中,在网络中心配置了 2 台思科 Catalyst 4506高性能核心交换机, 互为热备份,实现数据的高速转发、 负载均衡、 流量控制、网络管理等功能。 2台 Catalyst 4506核心交换机通过引擎上的 2个千兆光口,采用 EtherChannel 技术捆绑相互连接,互联带宽可达 4Gbps。两者之间通过 HSRP协议或者 VRRP 协议传递管理信息, 互为热备份, 确保业务持续稳定的运行。 在实现数据的高速 转发的同时,单台设备一旦发生故障, 在线进程可以被正常运行的另一台核心交 换机平滑接管, Session不会出现中断的情况,这样就不会影响全网的运行状态, 确保了系统

CPU在Cache中找到有用的数据被称为命中,当Cache中没有CPU所需的数据时(这时称为未命中),CPU才访问内存。从理论上讲,在一颗拥有2级Cache的CPU中,读取L1Cache的命中率为80%。也就是说CPU从L1Cache中找到的有用数据占数据总量的80%,剩下的20%从L2Cache读取。由于不能准确预测将要执行的数据,读取L2的命中率也在80%左右(从L2读到有用的数据占总数据的16%)。那么还有的数据就不得不从内存调用,但这已经是一个相当小的比例了。在一些高端领域的CPU中,我们常听到L3Cache,它是为读取L2Cache后未命中的数据设计的-种Cache,在拥有L3Cache的CPU中,只有约5%的数据需要从内存中调用,这进一步提高了CPU的效率。

为了保证CPU访问时有较高的命中率,Cache中的内容应该按一定的算法替换。一种较常用的算法是"最近最少使用算法"(LRU算法),它是将最近一段时间内最少被访问过的行淘汰出局。因此需要为每行设置一个计数器,LRU算法是把命中行的计数器清零,其他各行计数器加1。当需要替换时淘汰行计数器计数值最大的数据行出局。这是一种高效、科学的算法,其计数器清零过程可以把一些频繁调用后再不需要的数据淘汰出Cache,提高Cache的利用率。

Cache的替换算法对命中率的影响。 当新的主存块需要调入Cache并且它的可用空间位置又被占满时,需要替换掉Cache的数据,这就产生了替换策略(算法)问题。根据程序局部性规律可知:程序在运行中,总是频繁地使用那些最近被使用过的指令和数据。这就提供了替换策略的理论依据。 替换算法目标就是使Cache获得最高的命中率。Cache替换算法是影响代理缓存系统性能的一个重要因素,一个好的Cache替换算法可以产生较高的命中率。常用算法如下:

(1)随机法(RAND法) 随机替换算法就是用随机数发生器产生一个要替换的块号,将该块替换出去,此算法简单、易于实现,而且它不考虑Cache块过去、现在及将来的使用情况,但是没有利用上层存储器使用的"历史信息"、没有根据访存的局部性原理,故不能提高Cache的命中率,命中率较低。

(2)先进先出法(FIFO法) 先进先出(First-In-First-Out,FIFO)算法。就是将最先进入Cache的信息块替换出去。FIFO算法按调入Cache的先后决定淘汰的顺序,选择最早调入Cache的字块进行替换,它不需要记录各字块的使用情况,比较容易实现,系统开销小,其缺点是可能会把一些需要经常使用的程序块(如循环程序)也作为最早进入Cache的块替换掉,而且没有根据访存的局部性原理,故不能提高Cache的命中率。因为最早调入的信息可能以后还要用到,或者经常要用到,如循环程序。此法简单、方便,利用了主存的"历史信息", 但并不能说最先进入的就不经常使用,其缺点是不能正确反映程序局部性原理,命中率不高,可能出现一种异常现象。

(3)近期最少使用法(LRU法) 近期最少使用(Least Recently Used,LRU)算法。这种方法是将近期最少使用的Cache中的信息块替换出去。该算法较先进先出算法要好一些。但此法也不能保证过去不常用将来也不常用。 LRU法是依据各块使用的情况,总是选择那个最近最少使用的块被替换。这种方法虽然比较好地反映了程序局部性规律,但是这种替换方法需要随时记录Cache中各块的使用情况,以便确定哪个块是近期最少使用的块。LRU算法相对合理,但实现起来比较复杂,系统开销较大。通常需要对每一块设置一个称为计数器的硬件或软件模块,用以记录其被使用的情况。

- 相关百科

- 相关知识

- 相关专栏

- L3 Cache

- L6钢

- L6铝合金

- L7805

- L7805CV

- L80油管

- Lab模式

- Lab色彩空间

- Lab表色系

- Lab颜色模型

- LabWindows/CVI数据采集与串口通信典型应用实例(含DVD光盘1张)

- Lagostina

- LAN8720A-CP-TR

- Lanpas(兰巴斯)

- LATF晶体及其布里渊散射效应在激光相位共轭中的应用

- LAVENNI

- 基于压电堆驱动器的喷嘴挡板式气体控制阀

- 磷铵技术改造五大磷肥工程的建议

- 以大豆油多元醇制备的硬质聚氨酯泡沫塑料的性能

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 应用模糊数学理论对公路工程建设项目方案的综合评价

- 可替代现有隔热保温材料的新型材料

- 以贯穿项目为核心载体的建筑工程技术专业素材库建设

- 多逆变器太阳能光伏并网发电系统的组群控制方法

- 影响萘高效减水剂与普通硅酸盐水泥适应性的关键因素

- 在全县非煤矿山和危化企业安全生产工作会议上的讲话

- 中国工程造价咨询业的发展趋势

- 支持并行工程和智能CAPP的制造资源建模技术

- 中共重庆市委重庆市人民政府关于建设平安重庆的决定

- 智能建筑工程报警与电视监控系统前端设备的安装施工

- 在“建筑节能与居住舒适”专题技术交流会议上的讲话

- 以MSP430FW427为核心的远程数字水表设计