MOS管

mos管是金属(metal)-氧化物(oxide)-半导体(semiconductor)场效应晶体管,或者称是金属-绝缘体(insulator)-半导体。MOS管的source和drain是可以对调的,他们都是在P型backgate中形成的N型区。在多数情况下,这个两个区是一样的,即使两端对调也不会影响器件的性能。这样的器件被认为是对称的。

MOS管基本信息

| 中文名称 | mos管 | 外文名称 | metal oxide semiconductor |

|---|---|---|---|

| 元素 | 氧化物(oxid) | 别称 | 金属-氧化物-半导体 |

| 型号 | 电压/电流 封装 | ||

1.开启电压VT

·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;

·标准的N沟道MOS管,VT约为3~6V;

·通过工艺上的改进,可以使MOS管的VT值降到2~3V。

2. 直流输入电阻RGS

·即在栅源极之间加的电压与栅极电流之比

·这一特性有时以流过栅极的栅流表示

·MOS管的RGS可以很容易地超过1010Ω。

3. 漏源击穿电压BVDS

·在VGS=0(增强型)的条件下 ,在增加漏源电压过程中使ID开始剧增时的VDS称为漏源击穿电压BVDS

·ID剧增的原因有下列两个方面:

(1)漏极附近耗尽层的雪崩击穿

(2)漏源极间的穿通击穿

·有些MOS管中,其沟道长度较短,不断增加VDS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的ID

4. 栅源击穿电压BVGS

·在增加栅源电压过程中,使栅极电流IG由零开始剧增时的VGS,称为栅源击穿电压BVGS。

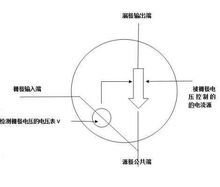

5. 低频跨导gm

·在VDS为某一固定数值的条件下 ,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

·gm反映了栅源电压对漏极电流的控制能力

·是表征MOS管放大能力的一个重要参数

·一般在十分之几至几mA/V的范围内

6. 导通电阻RON

·导通电阻RON说明了VDS对ID的影响 ,是漏极特性某一点切线的斜率的倒数

·在饱和区,ID几乎不随VDS改变,RON的数值很大,一般在几十千欧到几百千欧之间

·由于在数字电路中 ,MOS管导通时经常工作在VDS=0的状态下,所以这时的导通电阻RON可用原点的RON来近似

·对一般的MOS管而言,RON的数值在几百欧以内

7. 极间电容

·三个电极之间都存在着极间电容:栅源电容CGS 、栅漏电容CGD和漏源电容CDS

·CGS和CGD约为1~3pF

·CDS约在0.1~1pF之间

8. 低频噪声系数NF

·噪声是由管子内部载流子运动的不规则性所引起的

·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化

·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)

·这个数值越小,代表管子所产生的噪声越小

·低频噪声系数是在低频范围内测出的噪声系数

·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小

MOS管造价信息

MOS管发热分析

做电源设计,或者做驱动方面的电路,难免要用到MOS管。MOS管有很多种类,也有很多作用。做电源或者驱动的使用,当然就是用它的开关作用。

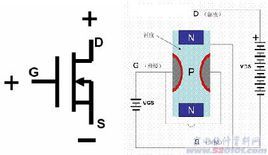

无论N型或者P型MOS管,其工作原理本质是一样的。MOS管是由加在输入端栅极的电压来控制输出端漏极的电流。MOS管是压控器件它通过加在栅极上的电压控制器件的特性,不会发生像三极管做开关时的因基极电流引起的电荷存储效应,因此在开关应用中,MOS管的开关速度应该比三极管快。其主要原理如图:图1。

图1 MOS管的工作原理

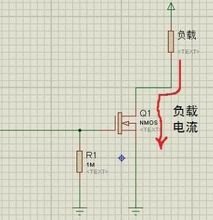

我们在开关电源中常用MOS管的漏极开路电路,如图2漏极原封不动地接负载,叫开路漏极,开路漏极电路中不管负载接多高的电压,都能够接通和关断负载电流。是理想的模拟开关器件。这就是MOS管做开关器件的原理。当然MOS管做开关使用的电路形式比较多了。

图2 NMOS管的开路漏极电路

在开关电源应用方面,这种应用需要MOS管定期导通和关断。比如,DC-DC电源中常用的基本降压转换器依赖两个MOS管来执行开关功能,这些开关交替在电感里存储能量,然后把能量释放给负载。我们常选择数百kHz乃至1MHz以上的频率,因为频率越高,磁性元件可以更小更轻。在正常工作期间,MOS管只相当于一个导体。因此,我们电路或者电源设计人员最关心的是MOS的最小传导损耗。

我们经常看MOS管的PDF参数,MOS管制造商采用RDS(ON)参数来定义导通阻抗,对开关应用来说,RDS(ON)也是最重要的器件特性。数据手册定义RDS(ON)与栅极(或驱动)电压VGS以及流经开关的电流有关,但对于充分的栅极驱动,RDS(ON)是一个相对静态参数。一直处于导通的MOS管很容易发热。另外,慢慢升高的结温也会导致RDS(ON)的增加。MOS管数据手册规定了热阻抗参数,其定义为MOS管封装的半导体结散热能力。RθJC的最简单的定义是结到管壳的热阻抗。

其发热情况有:

1.电路设计的问题,就是让MOS管工作在线性的工作状态,而不是在开关状态。这也是导致MOS管发热的一个原因。如果N-MOS做开关,G级电压要比电源高几V,才能完全导通,P-MOS则相反。没有完全打开而压降过大造成功率消耗,等效直流阻抗比较大,压降增大,所以U*I也增大,损耗就意味着发热。这是设计电路的最忌讳的错误。

2.频率太高,主要是有时过分追求体积,导致频率提高,MOS管上的损耗增大了,所以发热也加大了。

3.没有做好足够的散热设计,电流太高,MOS管标称的电流值,一般需要良好的散热才能达到。所以ID小于最大电流,也可能发热严重,需要足够的辅助散热片。

4.MOS管的选型有误,对功率判断有误,MOS管内阻没有充分考虑,导致开关阻抗增大。

MOS管定义

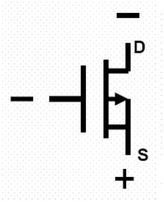

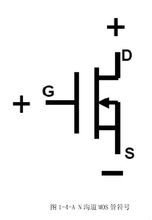

双极型晶体管把输入端电流的微小变化放大后,在输出端输出 一个大的电流变化。双极型晶体管的增益就定义为输出输入电流之比(beta)。另一种晶体管,叫做场效应管(FET),把输入电压的变化转化为输出电流的变化。FET的增益等于它的transconductance, 定义为输出电流的变化和输入电压变化之比。市面上常有的一般为N沟道和P沟道,详情参考右侧图片(N沟道耗尽型MOS管)。而P沟道常见的为低压mos管。

场效应管通过投影 一个电场在一个绝缘层上来影响流过晶体管的电流。事实上没有电流流过这个绝缘体,所以FET管的GATE电流非常小。最普通的FET用一薄层二氧化硅来作为GATE极下的绝缘体。这种晶体管称为金属氧化物半导体(MOS)晶体管,或,金属氧化物半导体场效应管(MOSFET)。因为MOS管更小更省电,所以他们已经在很多应用场合取代了双极型晶体管。

MOS管常见问题

-

MOS管一般又叫场效应管,与二极管和三极管不同,二极管只能通过正向电流,反向截止,不能控制,三极管通俗讲就是小电流放大成受控的大电流,MOS管是小电压控制电流的。MOS管的输入电阻极大,兆欧级的,容易...

-

MOS管的作用 MOS管为压控元件,你只要加到它的压控元件所需电压就能使它导通,它的导通就像三极管在饱和状态一样,导通结的压降最小.这就是常说的精典是开关作用.去掉这个控制电压经就截止. MOS管 M...

-

三极管工作时,有两种载流子流过PN结,所以它是有两种载流子参与导电的器件。mos管工作时,源漏极之间只有一种载流子参与导电,栅源极、栅漏极之间没有载流子流过,所以它是只有一种载流子参与导电的器件。所以...

首先考察一个更简单的器件--MOS电容--能更好的理解MOS管。这个器件有两个电极,一个是金属,另一个是extrinsic silicon(外在硅),他们之间由一薄层二氧化硅分隔开。金属极就是GATE,而半导体端就是backgate或者body。他们之间的绝缘氧化层称为gate dielectric(栅介质)。图示中的器件有一个轻掺杂P型硅做成的backgate。这个MOS 电容的电特性能通过把backgate接地,gate接不同的电压来说明。MOS电容的GATE电位是0V。金属GATE和半导体BACKGATE在WORK FUNCTION上的差异在电介质上产生了一个小电场。在器件中,这个电场使金属极带轻微的正电位,P型硅负电位。这个电场把硅中底层的电子吸引到表面来,它同时把空穴排斥出表面。这个电场太弱了,所以载流子浓度的变化非常小,对器件整体的特性影响也非常小。

当MOS电容的GATE相对于BACKGATE正偏置时发生的情况。穿过GATE DIELECTRIC的电场加强了,有更多的电子从衬底被拉了上来。同时,空穴被排斥出表面。随着GATE电压的升高,会出现表面的电子比空穴多的情况。由于过剩的电子,硅表层看上去就像N型硅。掺杂极性的反转被称为inversion,反转的硅层叫做channel。随着GATE电压的持续不断升高,越来越多的电子在表面积累,channel变成了强反转。Channel形成时的电压被称为阈值电压Vt。当GATE和BACKGATE之间的电压差小于阈值电压时,不会形成channel。当电压差超过阈值电压时,channel就出现了。

MOS电容:(A)未偏置(VBG=0V),(B)反转(VBG=3V),(C)积累(VBG=-3V)。

正是当MOS电容的GATE相对于backgate是负电压时的情况。电场反转,往表面吸引空穴排斥电子。硅表层看上去更重的掺杂了,这个器件被认为是处于accumulation状态了。

MOS电容的特性能被用来形成MOS管。Gate,电介质和backgate保持原样。在GATE的两边是两个额外的选择性掺杂的区域。其中一个称为source,另一个称为drain。假设source 和backgate都接地,drain接正电压。只要GATE对BACKGATE的电压仍旧小于阈值电压,就不会形成channel。Drain和backgate之间的PN结反向偏置,所以只有很小的电流从drain流向backgate。如果GATE电压超过了阈值电压,在GATE电介质下就出现了channel。这个channel就像一薄层短接drain和source的N型硅。由电子组成的电流从source通过channel流到drain。总的来说,只有在gate 对source电压V 超过阈值电压Vt时,才会有drain电流。

在对称的MOS管中,对source和drain的标注有一点任意性。定义上,载流子流出source,流入drain。因此Source和drain的身份就靠器件的偏置来决定了。有时晶体管上的偏置电压是不定的,两个引线端就会互相对换角色。这种情况下,电路设计师必须指定一个是drain另一个是source。

Source和drain不同掺杂不同几何形状的就是非对称MOS管。制造非对称晶体管有很多理由,但所有的最终结果都是一样的。一个引线端被优化作为drain,另一个被优化作为source。如果drain和source对调,这个器件就不能正常工作了。

晶体管有N型channel所有它称为N-channel MOS管,或NMOS。P-channel MOS(PMOS)管也存在,是一个由轻掺杂的N型BACKGATE和P型source和drain组成的PMOS管。如果这个晶体管的GATE相对于BACKGATE正向偏置,电子就被吸引到表面,空穴就被排斥出表面。硅的表面就积累,没有channel形成。如果GATE相对于BACKGATE反向偏置,空穴被吸引到表面,channel形成了。因此PMOS管的阈值电压是负值。由于NMOS管的阈值电压是正的,PMOS的阈值电压是负的,所以工程师们通常会去掉阈值电压前面的符号。一个工程师可能说,"PMOS Vt从0.6V上升到0.7V", 实际上PMOS的Vt是从-0.6V下降到-0.7V。

型号 电压/电流 封装

2N7000 60V,0.115A TO-92

2N7002 60V,0.2A SOT-23

IRF510A 100V,5.6A TO-220

IRF520A 100V,9.2A TO-220

IRF530A 100V,14A TO-220

IRF540A 100V,28A TO-220

IRF610A 200V,3.3A TO-220

IRF620A 200V,5A TO-220

IRF630A 200V,9A TO-220

IRF634A 250V,8.1A TO-220

IRF640A 200V,18A TO-220

IRF644A 250V,14A TO-220

IRF650A 200V,28A TO-220

IRF654A 250V,21A TO-220

IRF720A 400V,3.3A TO-220

IRF730A 400V,5.5A TO-220

IRF740A 400V,10A TO-220

IRF750A 400V,15A TO-220

IRF820A 500V,2.5A TO-220

IRF830A 500V,4.5A TO-220

IRF840A 500V,8A TO-220

IRFP150A 100V,43A TO-3P

IRFP250A 200V,32A TO-3P

IRFP450A 500V,14A TO-3P

IRFR024A 60V,15A D-PAK

IRFR120A 100V,8.4A D-PAK

IRFR214A 250V,2.2A D-PAK

IRFR220A 200V,4.6A D-PAK

IRFR224A 250V,3.8A D-PAK

IRFR310A 400V,1.7A D-PAK

MOS管文献

MOS管的构造及MOS管种类和结构

MOS管的构造及MOS管种类和结构

MOS 管的构造及 MOS 管种类和结构 随着社会的进步和发展, MOS 管在电子行业的应用越来越广泛,萨科微电子 SLKOR 作为能够研发生产碳化硅 SiC 产品的“碳化硅专家”,必须来科普一下这方面的知 识。 MOS 即 MOSFET 的简写,全称是金属氧化物场效应晶体管。 就是利用输入回路的电场效 应来控制输出回路电流的一种半导体器件。 MOS 管的构造、原理、特性、符号规则和封 装种类等,大致如下。 1、MOS 管的构造: MOS 管的构造是在一块掺杂浓度较低的 P 型半导体硅衬底上,用半导体光刻、扩散工艺 制作两个高掺杂浓度的 N+区,并用金属铝引出两个电极,分别作为漏极 D 和源极 S。然 后在漏极和源极之间的 P型半导体表面复盖一层很薄的二氧化硅( Si02)绝缘层膜,在再 这个绝缘层膜上装上一个铝电极,作为栅极 G。这就构成了一个 N 沟道(NPN 型)增强 型 MOS 管

mos管设计

mos管设计

1.共源放大器: 0V C3 10u RL 40k 0A 0V RD 50k 90.49uA 0V C1 10u Vsig 1Vac 0Vdc 0A 0V V2 5Vdc 90.49uA C2 10uM1 M2N6659 0A 90.49uA 0 0V 0 i 0V RG 10MEG 0A 0 0 475.4mV Rsig 1MEG0A 0 Vo -1.833V V1 5Vdc 90.49uA Vi 5.000V RS 35k 90.49uA 由图可知 MOS管偏置点电压 VGS=1.833V ,电流 ID=90.49uA , 由 output 中 的数据知 Vt=1.8V . Ro=3.5M Ω可求得跨 导 gm=2ID/(VGS-Vt)=5.484mA/V. 可 求 增 益 Gv=gm*(Ro||RD||RL ) *RG/(RG+Rsig)=109.09V/V; Av=gm*(Ro|

mos晶体管简介

MOS晶体管金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。MOS管构成的集成电路称为MOS集成电路,而PMOS管和NMOS管共同构成的互补型MOS集成电路即为CMOS-IC。

金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。MOS管构成的集成电路称为MOS集成电路,而PMOS管和NMOS管共同构 成的互补型MOS集成电路即为CMOS-IC

改变栅压可以改变沟道中的电子密度,从而改变沟道的电阻。这种MOS场效应晶体管称为P沟道增强型场效应晶体管。如果N型硅衬底表面不加栅压就已存在P型反型层沟道,加上适当的偏压,可使沟道的电阻增大或减小。这样的MOS场效应晶体管称为P沟道耗尽型场效应晶体管。统称为PMOS晶体管。

P沟道MOS晶体管的空穴迁移率低,因而在MOS晶体管的几何尺寸和工作电压绝对值相等的情况下,PMOS晶体管的跨导小于N沟道MOS晶体管。此外,P沟道MOS晶体管阈值电压的绝对值一般偏高,要求有较高的工作电压。它的供电电源的电压大小和极性,与双极型晶体管——晶体管逻辑电路不兼容。PMOS因逻辑摆幅大,充电放电过程长,加之器件跨导小,所以工作速度更低,在NMOS电路(见N沟道金属—氧化物—半导体集成电路)出现之后,多数已为NMOS电路所取代。只是,因PMOS电路工艺简单,价格便宜,有些中规模和小规模数字控制电路仍采用PMOS电路技术。

PMOS集成电路是一种适合在低速、低频领域内应用的器件。PMOS集成电路采用-24V电压供电。如图1所示的CMOS-PMOS接口电路采用两种电源供电。采用直接接口方式,一般CMOS的电源电压选择在10~12V就能满足PMOS对输入电平的要求。

MOS场效应晶体管具有很高的输入阻抗,在电路中便于直接耦合,容易制成规模大的集成电路。

N沟MOS晶体管简介

金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。MOS管构 成的集成电路称为MOS集成电路,而PMOS管和NMOS管共同构成的互补型MOS集成电路即为CMOS-IC。

由p型衬底和两个高浓度n扩散区构成的MOS管叫作n沟道MOS管,该管导通时在两个高浓度n扩散区间形成n型导电沟道。n沟道增强型MOS管必须在栅极上施加正向偏压,且只有栅源电压大于阈值电压时才有导电沟道产生的n沟道MOS管。n沟道耗尽型MOS管是指在不加栅压(栅源电压为零)时,就有导电沟道产生的n沟道MOS管。

NMOS集成电路是N沟道MOS电路,NMOS集成电路的输入阻抗很高,基本上不需要吸收电流,因此,CMOS与NMOS集成电路连接时不必考虑电流的负载问题。NMOS集成电路大多采用单组正电源供电,并且以5V为多。CMOS集成电路只要选用与NMOS集成电路相同的电源,就可与NMOS集成电路直接连接。不过,从NMOS到CMOS直接连接时,由于NMOS输出的高电平低于CMOS集成电路的输入高电平,因而需要使用一个(电位)上拉电阻R,R的取值一般选用2~100KΩ。

- 相关百科

- 相关知识

- 相关专栏

- 磷酸铁锂实验电炉

- mos晶体管

- 稳压管

- 双壁热缩管

- 晶体管毫伏表

- 散热片加热管

- 信息型光源

- 桃花心木亚科

- 带阻三极管

- 陶瓷电加热管

- 双转子锤式超细破碎机

- 玻璃放电管

- N沟MOS晶体管

- 碱性氮测定仪

- 304不锈钢焊接管

- 单头加热管

- 中华华丹雨、污水管道沟槽开挖专项施工方案教学教材

- 云计算技术在城市轨道交通运营指挥管理系统中的应用

- 圆管涵工程数量表(20201022195115)

- 园林绿化养护精细化管理对河源市园林景观的影响分析

- 云南省昆明市建设局建筑工程深基坑施工安全管理规定

- 原来这就是辨别冷热水管正确方法商家终于肯说实话了

- 中国施工企业管理协会科学技术奖技术创新成果申报书

- 支持群体设计的工程数据库管理系统的结构及实现

- 水利管理单位信访工作

- 圆CFRP-钢管混凝土偏压构件荷载-变形关系分析

- 中国石化北京设计院标准工艺装置管道垫片选用规定

- 以建筑工程资料管理的规范化促进工程质量的管理监督

- 中国家具钢管行业市场前景分析预测年度报告(目录)

- 有关建筑工程造价管理面临的问题与其处理手段

- 永春县农田水利设施产权制度改革和运行管护机制试点

- 以BIM为基础的装配式建筑全生命周期管理问题