低功耗高推力电磁线圈

低功耗高推力电磁线圈,是带有一种可瞬间提高电磁力然后仅仅保持工作所需的微功耗的芯片,塑封在普通电磁线圈中,这是一种目前比较先进的线圈内带有芯片的电磁线圈,该线圈在原数据不变的情况下,电磁吸力会得到大幅提升,电磁线圈温升明显减小,线圈工作功率明显下降等优点。该新型线圈的诞生使高压阀工作压力更高,尤其是大功率线圈温升明显下降,超低功率工作,但电磁线圈在阀上面的拉推力更大等,并且无交流电流噪声,因此可以长时间通电工作。

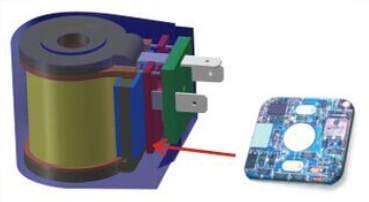

低功耗高推力电磁线圈图片

低功耗高推力电磁线圈概述

工作原理及作用:低功耗高推力电磁线圈,是带芯片塑封电磁线圈,这是一种目前比较先进的线圈内带有芯片的电磁线圈,该线圈在原数据不变的情况下,电磁吸力会得到大幅提升,电磁线圈温升明显减小,线圈工作功率明显下降等优点。该新型线圈的诞生使高压阀工作压力更高,尤其是大功率线圈温升明显下降,超低功率工作,但电磁线圈在阀上面的拉推力更大等,并且无交流电流噪声,因此可以长时间通电工作。

应用:

新型低功耗高推力电磁线圈用于电磁阀的特点:

1.适用于交流/直流各类电磁阀,电压一样,交直流可以通用。

2.不改变原电磁阀的结构

3.减小电磁阀的工作功率,为原来线圈功率的1/4

4.线圈长时间工作不发热,使用寿命超长

5:电磁线圈输出拉力增强3倍以上,响应速度变快

6:大幅度降低控制器电源的功率

7:交流电磁阀工作时无噪声音

低功耗高推力电磁线圈造价信息

低功耗高推力电磁线圈常见问题

-

哦,这是电磁吸盘的设计问题。你问问岳阳大力神,他们专业制造各种电磁铁,老板都是高工。

-

电磁线圈就是所谓的用于产生电磁的线圈。为发电机等(利用电磁感应原理工作的电气设备)提供工作磁场叫励磁。有时向发电机转子提供转子电源的装置也叫励磁。电磁线圈原理:是利用通过导线周围存在磁场而建立的,把它...

-

磁场与线圈的匝数成正比,所以线圈越长,不是考虑电阻电流,而是与匝数的关系!

低功耗高推力电磁线圈文献

舰载导弹电磁线圈垂直发射方案设计

舰载导弹电磁线圈垂直发射方案设计

目前和未来一段时期内,国内外的导弹发射基本方式仍然是倾斜热发射和垂直"热"、"冷"发射,这些发射方式在不同程度上存在反应时间长、性价比不高、容易暴露等不足。为了适应未来战争需要,提出了一种新型舰载导弹电磁线圈垂直发射器,阐述了该发射器的结构组成和发射机理,建立了其物理模型和数学模型。分析了发射器系统参数的设计流程,提出了系统参数设计方案;以某型舰载导弹的发射要求为指标,利用建立的动态仿真模型计算确定了该发射器的结构和电路参数,实现了导弹电磁发射方案的设计。

空调电磁离合器线圈烧毁

空调电磁离合器线圈烧毁

故障现象 一辆上海桑塔纳轿车,热天行车时,空调电磁离合器线圈突然被烧毁。为尽快修复,在维修时又换上一个新的电磁离合器线圈。但只行驶了1500km左右,电磁离合器线圈又被烧毁。

线圈配置的系列工业流体电磁阀特点:相比电磁阀,下一代电磁阀流量大,工作压力高,线圈温升低,不发热,可超长时间长期工作,工作功率低,便于设计大口径,高压力,低功耗的电磁阀,而不需要大功率线圈配置。做到节能又提高技术性能的电磁阀新的设计与应用。

一:产品用途

二位二通电磁阀系列,是自动控制系统中常见的执行器件,广泛应用于对各种流体如水、热水、气体液体、燃气、轻油等介质在管路中的自动启闭,可以长期工作,达到系统和设备的程序控制或远程及无线控制等。

二:工作原理

常闭型系列电磁阀,断电时呈关闭状态,当线圈通电时产生高电磁力,使活动铁芯克服弹簧力和固定铁芯吸合直接开启,打开阀口,介质呈现通路,当线圈断电时电磁力消失,动铁芯在弹簧力的作用下复位,直接关闭阀口,介质不通。结构简单,动作可靠,在零压力差和微真空下也可以正常工作。

这是一种 带芯片设计的电磁线圈,可提高产品的开阀性能(线圈电磁力增大),可在同等功率线圈下实测工作保持功率下降至原功率的20%,真正达到节能效果。线圈温升比原功率温升降低至20%,保证了电磁线圈的长寿命工作。2100433B

SM型线圈配置的系列工业流体电磁阀特点:相比目前的电磁阀,下一代电磁阀流量大,工作压力高,线圈温升低,不发热,可超长时间长期工作,工作功率低,便于设计大口径,高压力,低功耗的电磁阀,而不需要大功率线圈配置。做到节能又提高技术性能的电磁阀新的设计与应用。

一:产品用途

SM二位二通电磁阀系列,是自动控制系统中常见的执行器件,广泛应用于对各种流体如水、热水、气体液体、燃气、轻油等介质在管路中的自动启闭,可以长期工作,达到系统和设备的程序控制或远程及无线控制等。

二:工作原理

SM常闭型系列电磁阀,断电时呈关闭状态,当线圈通电时产生高电磁力,使活动铁芯克服弹簧力和固定铁芯吸合直接开启,打开阀口,介质呈现通路,当线圈断电时电磁力消失,动铁芯在弹簧力的作用下复位,直接关闭阀口,介质不通。结构简单,动作可靠,在零压力差和微真空下也可以正常工作。

这是一种 带芯片设计的电磁线圈,可提高产品的开阀性能(线圈电磁力增大),可在同等功率线圈下实测工作保持功率下降至原功率的20%,真正达到节能效果。线圈温升比原功率温升降低至20%,保证了电磁线圈的长寿命工作。

低功耗设计足一个复杂的综合性课题,就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。

动态电压调节

动态功耗与工作电压的平方成正比,功耗可随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS(Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。

两种时钟

在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性可以对降低整个系统的功耗产生很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

另一种常用的时钟技术就是可变频率时钟。它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

两种技术

并行结构的原理是通过牺牲面积来降低功耗。将一个功能模块复制为n(n≥2)个相同的模块,这些模块并行计算后通过数据选择器选择输出,采用二分频的并行结构。

并行设计后,由于有多个模块同时工作,提高了吞吐能力,可以把每个模块的速度降低为原来的l/n。根据延时和工作电压的线性关系,工作电压可以相应降低为原来的l/n,电容增大为原来的n倍,工作频率降低为原来的l/n,根据式(1)功耗降低为原来的1/n2。并行设计的关键是算法设计,一般算法中并行计算的并行度往往比较低,并行度高的算法比较难开发。例如:若原模块的功耗为P=a×CL×V2dd×f,采用二分频结构,由于增加了一个模块和数据选择器,整个电容负载为2.2CL,工作频率为f/2,工作电压可以降为O.6 V。由此可见,二分频并行结构在保持原有电路性能的同时降低了60%的功耗。

流水线技术本质上也是一种并行。把某一功能模块分成n个阶段进行流水作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器。若工作频率不变,对某个模块的速度要求仅为原来的1/n,则工作电压可以降低为原来的1/n,电容的变化不大(寄存器面积占的比例很小),功耗可降低为原来的1/n2,面积基本不变,但增加了控制的复杂度。例如,若原模块的功耗为P=α×C1×V2dd×f,采用流水线技术,由于增加了寄存器,整个电容负载为1.2CL,工作频率不变,工作电压降为0.6 V。由此可见,流水线技术能显著降低系统功耗。

通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。在深亚微米工艺下,工作电压已经比较接近阈值电压,为了使工作电压有足够的下降空间,应该降低阔值电压;但是随着阈值电压的降低,亚阈值电流可能呈指数增长,静态功耗迅速增加。因此,电压的下降空间有限。

低功耗单元库

设计低功耗单元库是降低功耗的一个重要方法,包括调整单元尺寸、改进电路结构和版图设计。用户可以根据负载电容和电路延时的需要选择不同尺寸的电路来实现,这样会导致不同的功耗,因此可以根据需要设计不同尺寸的单元。同时,为常用的单元选择低功耗的实现结构,如触发器、锁存器和数据选择器等。

状态机编码

状态机编码对信号的活动性具有重要影响,通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。其原则是:对于频繁切换的相邻状态,尽量采用相邻编码。例如:Gray码在任何两个连续的编码之间只有一位的数值不同,在设计计数器时,使用Gray码取代二进制码,则计数器的改变次数几乎减少一半,显著降低了功耗;在访问相邻的地址空间时,其跳变次数显著减少,有效地降低了总线功耗。

低功耗设计

作为现代微处理器中的重要部件,Cache的功耗约占整个芯片功耗的30%~60%,因此设计高性能、低功耗的Cach结构,对降低微处理器的功耗有明显作用。Cache低功耗设计的关键在于降低失效率,减少不必要的操作。通常用来降低Cache功耗的方法有以下两种:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。

以上主要是从硬件的角度来实现功耗的降低。除了硬件方法,通过软件方面的优化,也能显著地降低功耗。例如:在Crusoe处理器中,采用高效的超长指令(VLIW)、代码融合(Code Morphing)技术、LongRun电源管理技术和RunCooler工作温度自动调节等创新技术,获得了良好的低功耗效果。

- 相关百科

- 相关知识

- 相关专栏

- 吉祥鸟陶瓷

- 聚烯烃热塑性弹性体

- 色木槭

- 注塑技术

- 伟业铝材

- 伟昌铝材

- 小通草

- 手把手教您绘制建筑施工图

- 上海黎青薄板冷焊机

- 振升铝材

- 手把手教你学电工技能

- 放电线圈

- 纸面镁质板

- 6061铝材

- 5A02铝材

- 简欧家具

- 影响萘高效减水剂与普通硅酸盐水泥适应性的关键因素

- 亿阳信通中标环城高速公路晋江至石狮段机电工程项目

- 中国水电路桥武邵高速公路六标项目质量检验试验计划

- 基于超磁致伸缩效应的新型液压高速开关阀

- 怡达快速电梯SCORE项目获国际劳工组织高度评价

- 乍嘉苏高速公路改性沥青SMA—13面层试验段施工

- 引入PPP模式的高标准农田建设及财政支持体系创新

- 以工作过程为导向构建高职建筑工程技术专业课程体系

- 在书香中沉睡——“川大河畔”高尚住宅小区景观设计

- 应用型人才培养模式下高校机电工程综合实践改革探索

- 高效率PWM/PFM自动切换升压转换器的设计

- 智能照明系统在高校教学楼建筑节能改造中的应用

- 以污泥、建筑垃圾为基料制备高强轻质发泡环保陶瓷板

- 乍嘉苏高速公路改性沥青SMA-13面层试验段施工

- 高度集成化导航接收机系统射频电路的设计与实现

- 张涿高速南水北调干渠特大桥主桥边跨现浇段预压施工