差分放大器

差分放大器基本信息

| 中文名 | 差分放大器 | 外文名 | differential amplifier |

|---|---|---|---|

| 作 用 | 把两个输入电压的差值加以放大 | 别 称 | 差动放大器 |

放大器电路,或称放大电路,能增加信号的输出功率。它透过电源取得能量来源,以控制输出信号的波形与输入信号一致,但具有较大的振幅。依此来讲,放大器电路亦可视为可调节的输出电源,用来获得比输入信号更强的输出信号。

放大器的四种基本类型是电压放大器、电流放大器、互导放大器和互阻放大器。进一步的区别在于输出是否是输入的线性或非线性表示。放大器也可以通过在信号链中的物理位置来分类。

差分放大器造价信息

-

电子放大器

-

运算放大器

差分放大器(英语:differential amplifier、difference amplifier,也称:差动放大器、差放),是一种将两个输入端电压的差以一固定增益放大的电子放大器。

差分放大器是一种常用的电子放大器(也称“功率放大器”,简称“功放”)和发射极耦合逻辑电路(英语:EmitterCoupledLogic, ECL)的输入级。若差放的两个输入为

通常以差模增益和共模增益的比值共模抑制比(common-moderejectionratio, CMRR)衡量差分放大器消除共模信号的能力:

由上式可知,当共模增益

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。

很多系统在差分放大器的一个输入端输入输入信号,另一个输入端输入反馈信号,从而实现负反馈。常用于电机或者伺服电机控制,以及信号放大。在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。

差分放大器常见问题

-

差分放大电路构成差分放大器。

-

怎么要这么问呢?差分放大器 = 差动放大器 只是表达文字上的不同而以.

-

由两个参数特性相同的晶体管用直接耦合方式构成的放大器。若两个输入端上分别输入大小相同且相位相同的信号时,输出为零,从而克服零点漂移。适于作直流放大器。差分放大器是一种将两个输入端电压的差以一固定增益放...

差分放大器文献

尺寸及版图设计对集成电路差分放大器性能的影响

尺寸及版图设计对集成电路差分放大器性能的影响

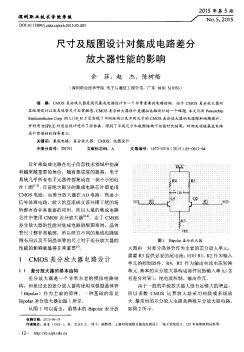

CMOS差分放大器是现代集成电路设计中一个非常重要的电路结构.由于CMOS差分放大器对其版图设计以及晶体管尺寸非常敏感,CMOS差分放大器设计是模拟电路设计的一个难题.本文利用Powerchip Semiconductor Corp的L110_N工艺实现了不同结构以及不同尺寸的CMOS差分放大器的电路图和版图设计,并利用HSPICE对这些设计进行了后仿真,得到了不同尺寸和版图结构下性能对比结果,对相关领域集成电路设计有很好的指导意义.

尺寸及版图设计对集成电路差分放大器性能的影响

尺寸及版图设计对集成电路差分放大器性能的影响

CMOS差分放大器是现代集成电路设计中一个非常重要的电路结构.由于CMOS差分放大器对其版图设计以及晶体管尺寸非常敏感,CMOS差分放大器设计是模拟电路设计的一个难题.本文利用PowerchipSemiconductorCorp的L110-N工艺实现了不同结构以及不同尺寸的CMOS差分放大器的电路图和版图设计,并利用HSPICE对这些设计进行了后仿真,得到了不同尺寸和版图结构下性能对比结果,对相关领域集成电路设计有很好的指导意义.

◇ 电路对称性——电路的对称性决定了被放大后的信号残存共模干扰的幅度,电路对称性越差,其共模抑制比就越小,抑制共模信号(干扰)的能力也就越差。

◇ 电路本身的线性工作范围——实际的电路其线性范围不是无限大的,当差模信号超出了电路线性范围时,即使正常信号也不能被正常放大,更谈不上共模抑制能力。实际电路的线性工作范围都小于其工作电压,这也就是为什么对共模抑制要求较高的设备前端电路也采用较高工作电压的原因。

差动放大器的一项重要功能是抑制两路输入的共模信号。如下图1所示,假设V2为5V,V1为3V,则4V为共模输入。V2比共模电压高1V,而V1低1V。二者之差为2V,因此R2/R1的“理想”增益施加于2V。如果电阻非理想,则共模电压的一部分将被差动放大器放大,并作为V1和V2之间的有效电压差出现VOUT,无法与真实信号相区别。差动放大器抑制这一部分电压的能力称为共模抑制(CMR)。该参数可以表示为比率的形式(CMRR),也可以转换为分贝(dB) 。

低功耗医疗仪器

传感器接口

热电偶放大器

工业过程控制

差分放大器

低功耗数据采集

整流电路是利用半导体二极管的单向导电性能把交流电变成单向脉动直流电的电路。

全波整流电路:一种具有第一和第二电源端子的全波整流电路,其第一和第二电源端子分别加有第一和第二电源电位,第一电源电位高于第二电源电位,其特征在于所述全波整流电路包括:差分放大器,具有在其间加有输入交流信号的第一和第二放大器输入端,用于差分地放大输入交流信号,所述差分放大器具有第一和第二放大器输出端,用于分别产生第一和第二放大的输出电压,二者彼此反相;电压参考电路,用于在第一和第二电源电位之间产生参考电压。

- 相关百科

- 相关知识

- 相关专栏

- 引上线

- 电门

- 零基础入门智能家居设计:基于C#语言与Proteus的实例应用

- 虚拟接地

- GB/T22520-2008厚度指示表

- JB/T7980-2010半径样板

- 电线电缆材料

- 佩尔顿式水轮机

- 《榻榻米》

- 阿拉斯加输油管

- 山墙

- 螺钉和螺母的装配工具术语

- 智能电表基础建设

- 衬环法兰

- 高压语音核相器

- 合成石材术语和分类

- 尺寸及版图设计对集成电路差分放大器性能的影响

- 基于压电堆驱动器的喷嘴挡板式气体控制阀

- 电气工程及其自动化特色专业建设探索

- 分形DGS单元结构设计及其在微带电路中的应用

- 磷铵技术改造五大磷肥工程的建议

- 以大豆油多元醇制备的硬质聚氨酯泡沫塑料的性能

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 预制砌块(砖、石)挡土墙工程砌体施工安全技术交底

- 应用模糊数学理论对公路工程建设项目方案的综合评价

- 引嫩工程扩建区土壤水盐动态与防治土壤盐碱措施

- 中华华丹雨、污水管道沟槽开挖专项施工方案教学教材

- 中国工程图学学会成立工程与制造系统集成化分会

- 中国吹制玻璃行业市场前景分析预测年度报告(目录)

- 可替代现有隔热保温材料的新型材料

- 医院病房楼工程施工装饰装修工程施工控制

- 在生活中构筑自然——河南天旺园林工程有限公司剪影