I2S

I2S(Inter-IC Sound)总线, 又称 集成电路内置音频总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专门用于音频设备之间的数据传输,广泛应用于各种多媒体系统。它采用了沿独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

I2S基本信息

| 中文名称 | I2S | 外文名称 | Inter-IC Sound |

|---|---|---|---|

| 别名 | 集成电路内置音频总线 | 发明公司 | 飞利浦公司 |

I2S总线概述

音响数据的采集、处理和传输是多媒体技术的重要组成部分。众多的数字音频系统已经进入消费市场,例如数字音频录音带、数字声音处理器。对于设备和生产厂家来说,标准化的信息传输结构可以提高系统的适应性。I2S(Inter-IC Sound)总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。它采用了沿独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

I2S造价信息

随着WS信号的改变,导出一个WSP脉冲信号,进入并行移位寄存器,从而输出数据被激活。串行数据的默认输入是0,因此所有位于最低位(LSB)后的数据将被设置为0。

随着第一个WS信号的改变,WSP在SCK信号的下降沿重设计数器。在"1 out of n"译码器对计数器数值进行译码后,第一个串行的数据(MSB)在SCK时钟信号的上升沿被存放进入B1,随着计数器的增长,接下来的数据被依次存放进入B2到Bn中。在下一个WS信号改变的时候,数据根据WSP脉冲的变化被存放进入左(声道)锁存器或者右(声道)锁存器,并且将B2一Bn的数据清除以及计数器重设,如果有冗余的数据则最低位之后的数据将被忽略。注意:译码器和计数器(虚线内的部分)可以被一个n比特移位寄存器所代替。

IIS总线接口可作为一个编码解码接口与外部8/16位的立体声音频解码电路(CODEC IC)相连,从而实现微唱片和便携式应用。它支持IIS数据格式和MSB-Justified 数据格式。IIS总线接口为先进先出队列FIFO的访问提供DMA传输模式来取代中断模式,可同时发送和接收数据,也可只发送或接收数据。

I2S(Inter-IC Sound)是飞利浦公司针对数字音频设备(如CD播放器、数码音效处理器、数字电视音响系统)之间的音频数据传输而制定的一种总线标准。它采用了独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。标准的I2S总线电缆是由3根串行导线组成的:1根是时分多路复用(简称TDM)数据线;1根是字选择线;1根是时钟线。

I2S常见问题

-

很抱歉,您咨询的I9400手机型号为非中国大陆上市版本。无法提供此款机器相关信息资料。

-

索尼x2i,价格1380元。现在已经是停产的了,其参数如下: 手机类型:3G手机 外观设计:侧滑盖 分辨率(像素):800×480 操作系统:Windows Mobile &n...

-

新12S4图集已发你邮箱,请注意查收!

在飞利浦公司的I2S标准中,既规定了硬件接口规范,也规定了数字音频数据的格式。

I2S有3个主要信号

1.串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数。

2. 帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为"1"表示正在传输的是右声道的数据,为"0"则表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

3.串行数据SDATA,就是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。

串行数据(SD)

I2S格式的信号无论有多少位有效数据,数据的最高位总是出现在LRCK变化(也就是一帧开始)后的第2个SCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

随着技术的发展,在统一的 I2S接口下,出现了多种不同的数据格式。根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐(较少使用)、I2S格式(即飞利浦规定的格式)和右对齐(也叫日本格式、普通格式)。

为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。当然,对I2S格式来说数据长度可以不同。

字段(声道)选择(WS)

命令选择线表明了正在被传输的声道。

WS=0,表示正在传输的是左声道的数据。

WS=1,表示正在传输的是右声道的数据。

WS可以在串行时钟的上升沿或者下降沿发生改变,并且WS信号不需要一定是对称的。在从属装置端,WS在时钟信号的上升沿发生改变。WS总是在最高位传输前的一个时钟周期发生改变,这样可以使从属装置得到与被传输的串行数据同步的时间,并且使接收端存储当前的命令以及为下次的命令清除空间。

电气规范:

输出电压:

VL <0.4V

VH>2.4V

输入电压

VIL<0.8V

VIH>2.0V

注:这是使用的TTL电平标准,随着其他IC(LSI)的流行,其他电平也会支持。

时序要求

在I2s总线中,任何设备都可以通过提供必需的时钟信号成为系统的主导装置,而从属装置通过外部时钟信号来得到它的内部时钟信号,这就意味着必须重视主导装置和数据以及命令选择信号之间的传播延迟,总的延迟主要由两部分组成:

1.外部时钟和从属装置的内部时钟之间的延迟

2.内部时钟和数据信号以及命令选择信号之间的延迟

对于数据和命令信号的输入,外部时钟和内部时钟的延迟不占据主导地位,它只是延长了有效的建立时间(set-up time)。延迟的主要部分是发送端的传输延迟和设置接收端所需的时间。

T是时钟周期,Tr是最小允许时钟周期,T>Tr这样发送端和接收端才能满足数据传输速率的要求。

对于所有的数据速率,发送端和接收端均发出一个具有固定的传号空号比(mark-space ratio)的时钟信号,所以t LC和tHC是由T所定义的。 t LC和tHC必须大于0.35T,这样信号在从属装置端就可以被检测到。

延迟(tdtr)和最快的传输速度(由Ttr定义)是相关的,快的发送端信号在慢的时钟上升沿可能导致tdtr不能超过tRC而使thtr为零或者负。只有tRC不大于tRCmax的时候(tRCmax>:0.15T),发送端才能保证thtr大于等于0。

为了允许数据在下降沿被记录,时钟信号上升沿及T相关的时间延迟应该给予接收端充分的建立时间(set-up time)。

数据建立时间(set-up time)和保持时间(hold time)不能小于指定接收端的建立时间和保持时间。

I2S文献

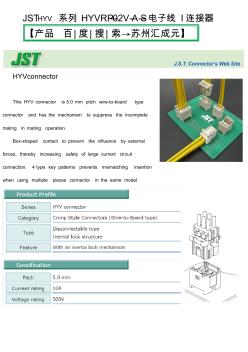

JSTHYV系列HYVRP-02V-A-S电子线I连接器【产品百I度I搜I索找→苏州汇成元】

JSTHYV系列HYVRP-02V-A-S电子线I连接器【产品百I度I搜I索找→苏州汇成元】

JSTHYV 系列 HYVRP‐02V‐A‐S电子线 I连接器 【产品 百 |度 |搜 |索→苏州汇成元】 HYVconnector This HYV connector is 5.0 mm pitch wire-to-board type connector and has the mechanism to suppress the incomplete mating in mating operation. Box-shaped contact to prevent the influence by external forces, thereby increasing safety of large current circuit connection. 4 type key patterns prevents mismatching insertion when using mul

S9.S11.S13变压器对比 (2)

S9.S11.S13变压器对比 (2)

S13-M-RL 型全密封油浸式电力变压器 1.产品介绍: S13-M-RL 型三相卷铁心全密封油浸式电力变压器是目前性能指标最优的节能型配电变压器产品。 S13 型 开口式立体卷铁心变压器是在 S11 卷铁心节能变压器的基础上推出的新产品,铁心呈三角形排列,铁心无 接缝,在专用的设备上卷绕成型,大大减少了磁阻,空载电流减少了 70~85% ,提高了功率因数,降低了 电网损耗,改善了电网的供电品质。卷铁心结构成自然紧固状态,无需夹件紧固,避免了因夹紧所带来的 性能恶化,所以空载损耗降低了 20~45% 。同时,卷铁心自身是一个无接缝的整体,且结构紧凑,在运行 时的噪声水平降低了 7~10dB ,非常适合于建筑物内和生活区安装使用。 我公司生产的 S13 型产品采用了优质硅钢片,全新的结构设计和生产工艺,采用全密封波纹片油箱结构设 计制造,外形美观,占地面积小,经济效益显著。 S13-M

M.2接口是一种兼容性十分广泛的微型接口,该接口可以通过设置其接口上的KEY槽,以实现不同功能的接口,M.2接口可以支持以下协议。

PCIe, PCIe LP

HSIC

SSIC

M-PCIe

USB

SDIO

UART

PCM/I2S

I2C

SMBus

SATA

Display Port

● Exynos4412 A9四核心处理器

● 标配1G DDR3 ARM (可选配2G)

● 标配4G eMMC (可选配16G)

● 二路YUV并行摄像头接口

● 一路24位RGB接口

● 二路PWM接口

● 一路HDMI接口

● 一路复位键

● 一路开机键(开机自启,请接地)

● 一路USB 2.0 OTG口

● 二路I2S接口

● 五路I2C总线接口

● 四路ADC接口

● 四路TTL 串口

● 一路电容式触摸屏接口

● 一路HSIC接口

● 二路SD卡接口

● 一路USB Host接口

● 一路以太网总线接口

● 二路SPI总线接口

● 二路1.8V输出接口

● 二路3.3V输出接口

● 28路外部中断口

● 16路GPIO接口

- 相关百科

- 相关知识

- 相关专栏

- 螺钿八宝花边方盒

- 香泡

- 输电导线

- 香泡树

- 组合导轮陶瓷导轮导线轮

- 管道清淤

- 香泡种子

- 明紫檀雕十八学士长方盒

- 檫木

- 1,2二硬酯酸-3磷脂酰乙醇胺

- 耐热导线应用技术

- 乙醇脲

- 水运仪象台

- 滑导线

- 无水氘代乙醇

- 三角高程导线

- 基于压电堆驱动器的喷嘴挡板式气体控制阀

- 电气工程及其自动化特色专业建设探索

- 分形DGS单元结构设计及其在微带电路中的应用

- 磷铵技术改造五大磷肥工程的建议

- 以大豆油多元醇制备的硬质聚氨酯泡沫塑料的性能

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 预制砌块(砖、石)挡土墙工程砌体施工安全技术交底

- 应用模糊数学理论对公路工程建设项目方案的综合评价

- 引嫩工程扩建区土壤水盐动态与防治土壤盐碱措施

- 中华华丹雨、污水管道沟槽开挖专项施工方案教学教材

- 中国工程图学学会成立工程与制造系统集成化分会

- 中国吹制玻璃行业市场前景分析预测年度报告(目录)

- 可替代现有隔热保温材料的新型材料

- 医院病房楼工程施工装饰装修工程施工控制

- 在生活中构筑自然——河南天旺园林工程有限公司剪影

- 中国机械工程学会授予材料热处理工程师资格人员名单