CMOS电平

CMOS电平逻辑电平电压接近于电源电压,0 逻辑电平接近于 0V。而且具有很宽的噪声容限。

CMOS电平基本信息

| 中文名称 | CMOS电平 | 外文名称 | Complementary Metal Oxide Semiconductor PMOS+NMOS |

|---|---|---|---|

| Vcc | 2.5V | 路 | 电压控制器件 |

CMOS电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片。

防御措施:

1)在输入端和输出端加钳位电路,使输入和输出不超过规定电压。

2)芯片的电源输入端加去耦电路,防止VDD端出现瞬间的高压。

3)在VDD和外电源之间加限流电阻,即使有大的电流也不让它进去。

4)当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启CMOS电路的电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭CMOS 电路的电源。

CMOS电平造价信息

1)TTL电路是电流控制器件,而CMOS电路是电压控制器件。

2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

CMOS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

CMOS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS

1 逻辑电平电压接近于电源电压,0 逻辑电平接近于 0V。而且具有很宽的噪声容限。

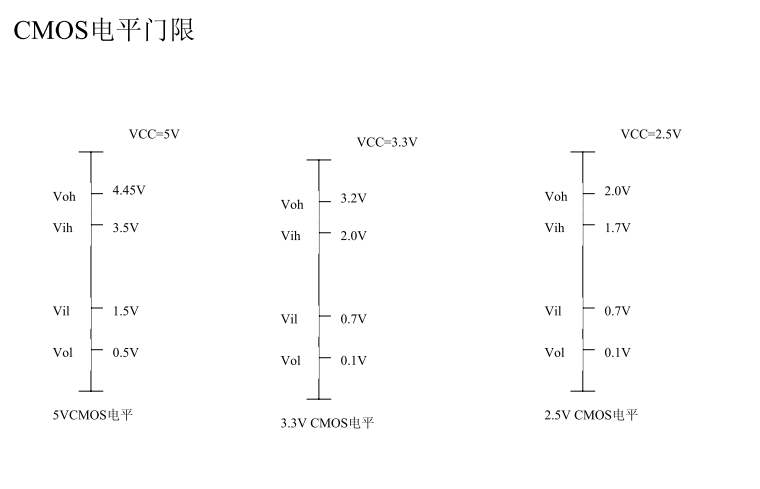

Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。

相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

3.3V LVCMOS:

Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。

2.5V LVCMOS:

Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

CMOS使用注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。

CMOS电平常见问题

-

TTL集成电路使用TTL管,也就是PN结。功耗较大,驱动能力强,一般工作电压+5V CMOS集成电路使用MOS管,功耗小,工作电压范围很大,一般速度也低,但是技术在改进,这已经不是问题。 就TTL与C...

-

电路中的电平标准(TTL,CMOS,232等等)是哪个组织规定的?

个人计算机上的通讯接口之一,由电子工业协会(Electronic Industries Association,EIA) 所制定的异步传输标准接口。通常 RS-232 接口以9个引脚 (DB-9) 或...

CMOS电平文献

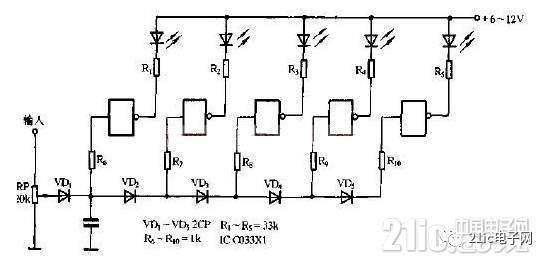

最新5-6CMOS电路汇总

最新5-6CMOS电路汇总

最新5-6CMOS电路汇总

CMOS光接收机前端放大电路

CMOS光接收机前端放大电路

利用SMIC 0.18μmCMOS工艺设计了光接收机前端放大电路.在前置放大器中,设计了一种高增益有源反馈跨阻放大器,并且可以使输出共模电平在较大范围内调解.在限幅放大器中,通过在改进的Cherry-Hooper结构里引入有源电感负反馈来进一步扩展带宽.整个前端放大电路具有较高的灵敏度和较宽的输入动态范围.Hspice仿真结果表明该电路具有119dB的中频跨阻增益,2.02GHz的带宽,对于输入电流幅度从1.4μA到170μA变化时,50Ω负载线上的输出电压限幅在320mV(V_(pp)),输出眼图稳定清晰.核心电路静态功耗为45.431mW.

1,TTL电平(什么是TTL电平):

TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑“1”,0V等价于逻辑“0”,这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。

TTL电平信号对于计算机处理器控制的设备内部的数据传输是很理想的,首先计算机处理器控制的设备内部的数据传输对于电源的要求不高以及热损耗也较低,另外TTL电平信号直接与集成电路连接而不需要价格昂贵的线路驱动器以及接收器电路;再者,计算机处理器控制的设备内部的数据传输是在高速下进行的,而TTL接口的操作恰能满足这个要求。TTL型通信大多数情况下,是采用并行数据传输方式,而并行数据传输对于超过10英尺的距离就不适合了。这是由于可靠性和成本两面的原因。因为在并行接口中存在着偏相和不对称的问题,这些问题对可靠性均有影响。 TTL电路不使用的输入端悬空为高电平。

输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

2,CMOS电平:

1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且具有很宽的噪声容限。 CMOS电路输出高电平约为0.9Vcc,而输出低电平约为 0.1Vcc。

CMOS电路不使用的输入端不能悬空,会造成逻辑混乱。

另外,CMOS集成电路电源电压可以在较大范围内变化,因而对电源的要求不像TTL集成电路那样严格。

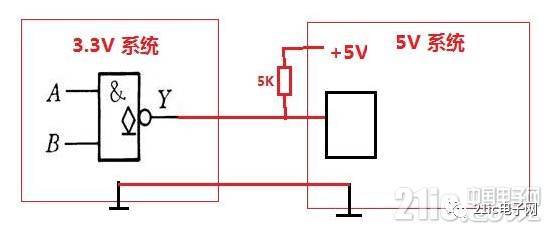

3,电平转换电路:

因为TTL和COMS的高低电平的值不一样(ttl 5v<==>cmos 3.3v),所以互相连接时需要电平的转换:就是用两个电阻对电平分压,没有什么高深的东西。哈哈

4,OC门

又称集电极开路与非门门电路,Open Collector(Open Drain)。实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:

1、实现与或非逻辑,用做电平转换,用做驱动器。由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。在硬件上,可用OC门或三态门(ST门)来实现。 用OC门实现线与,应同时在输出端口应加一个上拉电阻。

3、三态门(ST门)主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

OD门,即漏极开路门电路open-drain,必须外界上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。开漏形式的电路有以下几个特点:

1)利用外部电路的驱动能力,减少IC内部的驱动。 或驱动比芯片电源电压高的负载.

2)可以将多个开漏输出的Pin,连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。这也是I2C,SMBus等总线判断总线占用状态的原理。如果作为图腾输出必须接上拉电阻。接容性负载时,下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢。如果要求速度高电阻选择要小,功耗会大。所以负载电阻的选择要兼顾功耗和速度。

3)可以利用改变上拉电源的电压,改变传输电平。例如加上上拉电阻就可以提供TTL/CMOS电平输出等。

4)开漏Pin不连接外部的上拉电阻,则只能输出低电平。一般来说,开漏是用来连接不同电平的器件,匹配电平用的。

5)正常的CMOS输出级是上、下两个管子,把上面的管子去掉就是OPEN-DRAIN了。这种输出的主要目的有两个:电平转换和线与。

6)由于漏级开路,所以后级电路必须接一上拉电阻,上拉电阻的电源电压就可以决定输出电平。这样你就可以进行任意电平的转换了。

7)线与功能主要用于有多个电路对同一信号进行拉低操作的场合,如果本电路不想拉低,就输出高电平,因为OPEN-DRAIN上面的管子被拿掉,高电平是靠外接的上拉电阻实现的。(而正常的CMOS输出级,如果出现一个输出为高另外一个为低时,等于电源短路。)

8)OPEN-DRAIN提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出。

5,TTL和COMS电路比较:

1)TTL电路是电流控制器件,而coms电路是电压控制器件。

2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

3)COMS电路的锁定效应:

COMS电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片。

防御措施: 1)在输入端和输出端加钳位电路,使输入和输出不超过不超过规定电压。

2)芯片的电源输入端加去耦电路,防止VDD端出现瞬间的高压。

3)在VDD和外电源之间加线流电阻,即使有大的电流也不让它进去。

4)当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启COMS电路得电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭COMS电路的电源。

6,COMS电路的使用注意事项

1)COMS电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强。所以,不用的管脚不要悬空,要接上拉电阻或者下拉电阻,给它一个恒定的电平。

2)输入端接低内组的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的电流限制在1mA之内。

3)当接长信号传输线时,在COMS电路端接匹配电阻。

4)当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为R=V0/1mA.V0是外界电容上的电压。

5)COMS的输入电流超过1mA,就有可能烧坏COMS。

7,TTL门电路中输入端负载特性(输入端带电阻特殊情况的处理):

1)悬空时相当于输入端接高电平。因为这时可以看作是输入端接一个无穷大的电阻。

2)在门电路输入端串联10K电阻后再输入低电平,输入端出呈现的是高电平而不是低电平。因为由TTL门电路的输入端负载特性可知,只有在输入端接的串联电阻小于910欧时,它输入来的低电平信号才能被门电路识别出来,串联电阻再大的话输入端就一直呈现高电平。这个一定要注意。COMS门电路就不用考虑这些了。

8,TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。

OC门在截止时有漏电流输出,那就是漏电流,为什么有漏电流呢?那是因为当三机管截止的时候,它的基极电流约等于0,但是并不是真正的为0,经过三极管的集电极的电流也就不是真正的 0,而是约0。而这个就是漏电流。开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。它可以吸收很大的电流,但是不能向外输出的电流。所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。OD门一般作为输出缓冲/驱动器、电平转换器以及满足吸收大负载电流的需要。

9,什么叫做图腾柱,它与开漏电路有什么区别?

TTL集成电路中,输出有接上拉三极管的输出叫做图腾柱输出,没有的叫做OC门。因为TTL就是一个三级关,图腾柱也就是两个三级管推挽相连。所以推挽就是图腾。一般图腾式输出,高电平400UA,低电平8MA。

本文转自网络,版权归原作者,如果您觉得不好,请联系我们删除!

广告

[导读] COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。

COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。

本文引用地址: http://www.21ic.com/app/analog/201709/736464.htm

COMS电路的供电电压VDD范围比较广在+5~+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑 1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑 0。CMOS电路输出高电平约为 0.9Vcc,而输出低电平约为 0.1Vcc.当输入电压高于VDD-1.5V时为逻辑 1,输入电压低于VSS+1.5V(VSS为数字地)为逻辑 0。

TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑“1”,0V等价于逻辑“0”,这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。

标准TTL输入高电平最小2V,输出高电平最小2.4V,典型值3.4V,输入低电平最大 0.8V,输出低电平最大 0.4V,典型值 0.2V(输入 H》2V,输入 L《0.8V;输出H 》2.4V(3.4V),输出L《0.4V(0.2V)。

CMOS电平是数字信号还是模拟信号?

CMOS电平是数字信号,COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0, 一般数字信号才是0和1 。

cmos电平转换电路

1、 TTL电路和CMOS电路的逻辑电平

VOH: 逻辑电平 1 的输出电压

VOL: 逻辑电平 0 的输出电压

VIH : 逻辑电平 1 的输入电压

VIH : 逻辑电平 0 的输入电压

TTL电路临界值:

VOHmin = 2.4V VOLmax = 0.4V VIHmin = 2.0V VILmax = 0.8V

CMOS电路临界值(电源电压为+5V)

VOHmin = 4.99V VOLmax = 0.01V VIHmin = 3.5V VILmax = 1.5V

2、TTL和CMOS的逻辑电平转换

CMOS电平能驱动TTL电平

TTL电平不能驱动CMOS电平,需加上拉电阻。

3、用逻辑芯片特点

74LS系列: TTL 输入: TTL; 输出:TTL

74HC系列:CMOS输入: CMOS; 输出:CMOS

74HCT系列: CMOS 输入:TTL; 输出: CMOS

CD4000系列: CMOS 输入: CMOS 输出: CMOS。

常用的几种电平转换方案

(1) 晶体管+上拉电阻法

就是一个双极型三极管或 MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。

(2) OC/OD 器件+上拉电阻法

跟 (1) 类似。适用于器件输出刚好为 OC/OD 的场合。

(3) 74xHCT系列芯片升压 (3.3V→5V)

凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换。

——这是由于 3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而 CMOS 的输出电平总是接近电源电平的。

廉价的选择如 74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/。。。) 系列 (那个字母 T 就表示 TTL 兼容)。

(4) 超限输入降压法 (5V→3.3V, 3.3V→1.8V, 。。。)

凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。

这里的“超限”是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。

例如,74AHC/VHC 系列芯片,其 datasheets 明确注明“输入电压范围为0~5.5V”,如果采用 3.3V 供电,就可以实现 5V→3.3V 电平转换。

(5) 专用电平转换芯片

最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

(6) 电阻分压法

最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。

(7) 限流电阻法

如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如 74HC 系列为 20mA),仍然是安全的。

1、控制器上标识的高低电平为刹车,高电平一般规定为5V以上,低电平为0V左右。

2、在不同电路上的电压值不相同,如果是5V供电的数字电路,高电平就是5V,或接近5V。低电平就是‘无’,就是0V或接近0V。

3、控制器的高电平是通,低电平是控 。

- 相关百科

- 相关知识

- 相关专栏

- 双向触发三极管

- 热封型双向拉伸聚丙烯薄膜

- 蓄电池双向电流检测

- 电动车双向报警器

- 双向防丢器

- 钢铁行业

- 95-2双向恒温磁力搅拌器

- 双向拉伸塑料薄膜

- 双向玻纤土工格栅

- 电动车双向防盗报警器

- 双向防盗

- 双向压蝶阀

- Bio-Rad双向电泳装置

- 荷兰隧道

- CKS型双向楔块超越离合器

- 双向密封无凹槽刀闸阀

- 用于电视调谐器的宽带CMOS低噪声放大器设计

- 基于CMOS工艺的二维风速传感器的设计和测试

- 基于单元串联多电平高压变频器异步电机直流制动

- 低压CMOS带隙基准电流源

- CMOS APS的星敏感器光学系统结构设计与优化

- 加箝位二极管的零电压开关PWM复合式全桥三电平变换器

- 半导体制冷型高帧频CMOS数字摄像机及其成像噪声分析

- 半桥三电平逆变器输出不对称交流时直流侧电容电压的分析

- CMOS集成电路中电源和地之间ESD保护电路设计

- 新型半桥电流源串联谐振软开关三电平逆变器及其控制

- 桥级联多电平变流器的直流母线电压平衡控制策略

- 二极管钳位型单相三电平逆变器空间矢量脉宽调制方法

- 单元串联多电平高压变频器开关量控制电路及功能设计

- 单元串联式多电平变频器在高压风机调速系统中的应用

- 12位100MSPS CMOS双采样保持电路

- LSF0108-Q1汽车类8通道多电压电平转换器