ARM工具网压板夹

特点

1、塑料柄带保护帽

2、木材加工,机器操作使用。

应用范围

广泛用于电力、钢铁、造船、石油化工、矿山、铁路、建筑、汽车制造、塑料机械、工业控制、管道辅设、边坡隧道、井道治理防护、海洋工程、机场建设、桥梁、场馆以及修理场所的理想工具。

ARM工具网造价信息

特点

1、高档日式尖嘴钳。

2、由于使用范围广,受到使用者的广泛好评!

3、尖嘴钳的两个手柄,容易握住,使用的手恰好适应!

用途

剪切线径较细的单股与多股线,以及给单股 导线接头弯圈、剥塑料绝缘层等,能在较狭小的工作空间操作,不带刃口者只能夹捏工作,带刃口者能翦切细小零件,它是电工(尤其是内线电工)、仪表及电讯器材等装配及修理工作的常用工具。

特点

1、完全的高频淬火,切割的锋利度出众。

2、精密的刃合

3、在电气通信机器及电子学等的线路工作最适合的工具。

4、拥有更容易握住的专业用把手。

ARM工具网压板夹常见问题

-

这到底怎样个形状要求呢?

-

垫板夹价格为15元,垫板夹使用起来是比较的好的,而且其垫板夹的形状是比较的多的,其在市场上的需求量是比较的多的,而且寻找起来还是比较的好的。

-

你可以把头发分成一缕一缕的顺着一个方向拧起劲,用直板夹在拧紧的头发上熨两下,每缕都这样做,就会像烫过一样的卷发了!

特点

1、剪刀头由优质弹簧钢制成,有极高的硬度和韧性,可剪断硬度为掺2的材料。

2、刃口锋利,耐磨,剪切阻力小。

3、高强度的坚固螺栓,配合防松螺母,全部经过特殊热处理。

4、手柄选择杜邦材料作为涂覆层,色彩鲜艳,经久耐用。

5、手柄与剪刀头本体紧密配合,牢固可靠。

6、PVC握把手感舒适。

应用范围

广泛用于电力、邮电、铁路、建筑、消防等施工、检修及野外高空、水下作业。

安全的注意事项

1、操作机器时,使用手套握住椭圆形的套筒。

2、其他压接工具,根据说明指示操作。如发生事故,可能短时间内无法承受重量

3、压接电线上有涂层,要去掉涂层。清除涂层,保持相应的重量。

4、为确保安全钢丝绳为两个以上时,请一定要遵守安全负荷。

应用范围

用于房屋建筑、轧钢厂、冶金、港口、电力、建筑、厂矿、场馆等重要行业以及基础建设工程的机械设备。

特点

1、新型油压拉马具有结构紧凑、使用灵活、携带操作方便省力

2、三爪式与二爪式可根据现场工作需要拆换。

3、可以自由旋转按拉马距离活塞中心点,很快可碰到被拉工件中心点。

4、可任意选配泵浦。

5、使用灵活、重量轻、体积小、携带方便。

应用范围

广泛用于港口、电力、钢铁、造船、石油化工、矿山、铁路、建筑、冶金化工、汽车制造、塑料机械、工业控制、公路、大件运输、管道辅设、边坡隧道、井道治理防护、海上救助、海洋工程、机场建设、桥梁、航空、航天、场馆以及修理场所的理想工具。

安全的注意事项

1、操作机器时,使用手套握住椭圆形的手柄。

2、其他压接工具,根据说明指示操作。如发生事故,可能短时间内无法承受重

3、压接电线上有涂层,要去掉涂层。清除涂层,保持相应的重量。

4、为确保安全钢丝绳为两个以上时,请一定要遵守安全负荷。

应用范围

用于房屋建筑、轧钢厂、石油、矿山、桥梁、隧道、电站、大型水利等工程。

特点

1、最轻便设计的充电式液压工具,可单手操作。

2、无绳液压断线钳,轻巧,耐用性高

3、到达设定压力自动卸压,头部可旋转。

4、切割钢筋75φ16mm,切割钢筋110φ13mm

5、材质是高速钢叶片涂层钛粉,机械式液压头质量高。

应用范围

配电作业压接端子,广泛用于电力、邮电、铁路、建筑、消防等施工、维修及野外高空。

特点

1、装有弹簧的自锁式钩形钳口,可供单手操作。

2、钩形钳口上标有尺寸,便于快速调整到具体管子尺寸

3、有环氧树脂粉末涂层,能防刮。

4、根据无氧热处理和高频淬火,保证出色的耐久力,能满足不同工作环境的多种需求。

用途

安装螺纹连接的暖气管和自来水管。

特点

1、手柄与手掌更多的接触面,确保力的高度传递;

2、人体工程学设计的手柄;

3、全新设计的外形和表面涂层,防止手柄间手指挤压;

4、手柄表面覆盖软橡胶,握感舒适,另有辅助支撑作用,传递最大力。

用途

1、齿口可用来紧固或拧松螺母;

2、刀口可用来剖切软电线的橡皮或塑料绝缘层,也可用来剪切电线、铁丝;

3、铡口可以用来切断电线、钢丝等较硬的金属线;

4、钳子的绝缘塑料管耐压500V以上,多用来起钉子或夹断钉子等;

钢丝钳、管子钳、电缆钳、电动液压断线钳、液压钳、液压钢筋切割机、液压钢丝切割机、油压拉玛器、椭圆套筒、断线钳、强力钳子、尖嘴钳、压板夹、压接钳、剪钳、剪线钳、充电式冲击钻、万能钳子。

特点

1、压接时轻松,很容易握的手柄的形状,费力少、作业效率好。

2、在使用同时也很方便,附带替换刀的柄部、可以简单调整。

3、品质好,刀部的锻造・可以烧、耐久性、和出色的清晰度

注意事项

1、电流流出来请不要使用。

2、切断能力超过线材请不要切。

ARM工具网压板夹文献

带螺旋导流板夹套容器设计

带螺旋导流板夹套容器设计

带螺旋导流板夹套容器设计

轻质条板夹芯保温填充墙的实验研究

轻质条板夹芯保温填充墙的实验研究

本文选择工业灰渣空心条板和保温芯材,设计研究了一种复合夹心墙填充墙技术。传统建筑墙体一般采用单一材料,如空心砌块墙体、砖墙、加气混凝土墙体等,单一材料导热系数太大,一般为聚氨酯保温材料的20倍,不能满足保温节能的新要求,因此往往采用承重墙体与高效保温材料组成复合墙体。复合墙体很好的发挥了两种材料的长处,既不会使墙体过厚,又能承重,保温效果优异。

---

有同学反映,我们视频一上来就讲干货,希望适当普及一下相关概念,这篇就是。

ARM处理器解析

ARM9、ARM11是哈佛5级流水线结构,所以性能要高一点。ARM9和ARM11大多带内存管理器,跑操作系统好一点,ARM7适合裸奔。我们惯称的 ARM9系列中又存在ARM9与ARM9E两个系列,其中ARM9 属于ARM v4T架构,典型处理器如ARM9TDMI和ARM922T;

而ARM9E属于ARM v5TE架构,典型处理器如ARM926EJ和ARM946E。因为后者的芯片数量和应用更为广泛,所以我们提到ARM9的时候更多地是特指ARM9E系列处理器(主要就是ARM926EJ和ARM946E这两款处理器)。

下面关于ARM9的介绍也是更多地集中于ARM9E。

2

ARM7处理器和ARM9E处理器的流水线差别

对嵌入式系统设计者来说,硬件通常是第一考虑的因素。针对处理器来说,流水线则是硬件差别的最明显标志,不同的流水线设计会产生一系列硬件差异。

让我们来比较一下ARM7和ARM9E的流水线,ARM9E从ARM7的3级流水线增加到了5级,ARM9E的流水线中容纳了更多的逻辑操作,但是每一级的逻辑操作却变得更为简单。

比如原来 ARM7的第三级流水,需要先内部读取寄存器、然后进行相关的逻辑和算术运算,接着处理结果回写,完成的动作非常复杂;

而在ARM9E的5级流水中,寄存器读取、逻辑运算、结果回写分散在不同的流水当中,使得每一级流水处理的动作非常简洁。这就使得处理器的主频可以大幅度地提高。因为每一级流水都对应 CPU的一个时钟周期,如果一级流水中的逻辑过于复杂,使得执行时间居高不下,必然导致所需的时钟周期变长,造成CPU的主频不能提升。所以流水线的拉长,有利于CPU主频的提高。

在常用的芯片生产工艺下,ARM7一般运行在100MHz左右,而ARM9E则至少在200MHz以上。

3

ARM9E处理器的存储器子系统

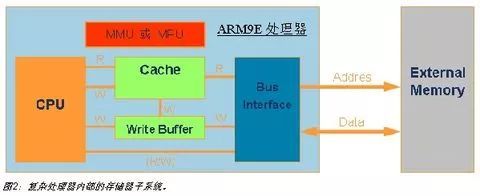

像ARM926EJ 和ARM946E这两个最常见的ARM9E处理器中,都带有一套存储器子系统,以提高系统性能和支持大型操作系统。如图2所示,一个存储器子系统包含一个 MMU(存储器管理单元)或MPU(存储器保护单元)、高速缓存(Cache)和写缓冲(Write Buffer);CPU通过该子系统与系统存储器系统相连。

高速缓存和写缓存的引入是基于如下事实,即处理器速度远远高于存储器访问速度;如果存储器访问成为系统性能的瓶颈,则处理器再快也是浪费,因为处理器需要耗费大量的时间在等待存储器上面。

高速缓存正是用来解决这个问题,它可以存储最近常用的代码和数据,以最快的速度提供给CPU处理(CPU访问Cache不需要等待)。

4

复杂处理器内部的存储器子系统

MMU则是用来支持存储器管理的硬件单元,满足现代平台操作系统内存管理的需要;它主要包括两个功能:一是支持虚拟/物理地址映射,二是提供不同存储器地址空间的保护机制。

一个简单的例子可以帮助我们理解MMU的功能,在一个操作系统下,程序开发人员都是在操作系统给定的API和编程模型下开发程序;操作系统通常只开放一个确定的存储器地址空间给用户。这样就带来 一个直接的问题,所有的应用程序都使用了相同的存储器地址空间,如果这些程序同时启动的话(在现在的多任务系统中这是非常常见的),就会产生存储器访问冲 突。那操作系统是如何来避免这个问题的呢?

操作系统会利用MMU硬件单元完成存储器访问虚拟地址到物理地址的转换。所谓虚拟地址就是程序员在程序中使用的逻辑地址,而物理地址则是真实存储器单元的空间地址。MMU通过一定的规则, 可以把相同的虚拟地址映射到不同的物理地址上去。这样,即使有多个使用相同虚拟地址的程序进程启动,也可以通过MMU调度把它们映射到不同的物理地址上 去,不会造成系统错误。

5

MMU的功能和作用

MMU 处理地址映射功能之外,还能给不同的地址空间设置不同的访问属性。比如操作系统把自己的内核程序地址空间设置为用户模式下不可访问,这样的话用户应用程序就无法访问到该空间,从而保证操作系统内核的安全性。

MPU与MMU的区别在于它只有给地址空间设置访问属性的功能而没有地址映射功能。Cache以及MMU等硬件单元的引入,给系统程序员的编程模型带来了许多全新的变化。

除了需要掌握基本的概念和使用方法之外,下面几个针对系统优化的点既有趣又重要:

1.系统实时性考虑因素

为保存地址映射规则的页表(Page Table)非常庞大,通常MMU中只是存储器了常用的一小段页表内容,大部分页表内容都存储于主存储器里面;当调用新的地址映射规则时,MMU可能需要读取主存储器来更新页表。

这在某些情况下会造成系统实时性的丢失。比如当需要执行一段关键的程序代码时,如果不巧这段代码使用的地址空间不在当前MMU的页表处理范围里面,则MMU首先需要更新页表,然后完成地址映射,接着才能相应存储器访问;

整个地址译码过程非常长,给实时性带来非常大的不利影响。所以一般来说带MMU和Cache的系统在实时性上不如一些简单的处理器;不过也有一些办法能够帮助提高这些系统的实时效率。

一个简单的办法是在需要的时候关闭MMU和Cache,这样就变成一个简单处理器了,可以马上提高系统实时性。当然很多情况下这不可行;

在ARM的MMU和 Cache设计中,有一个锁定的功能,就是说你可以指定某一块页表在MMU中不会被更新掉,某一段代码或数据可以在Cache中锁定而不会被刷新掉;程序员可以利用这个功能来支持那些实时性要求最高的代码,保证这些代码始终能够得到最快的响应和支持。

2.系统软件优化

在嵌入式系统开发中,很多系统软件优化的方法都是相同和通用的,多数情况下这种规则也适用于ARM9E架构上。如果你已经是一个ARM7的编程高手,那么恭喜你,以前你掌握的优化方法完全可以用在新的ARM9E平台上,但是会有一些新的特性需要你加倍注意。最重要的便是Cache的作用,Cache本身并不 带来编程模型和接口的变化,但是如果我们考察Cache的行为,就能够发现对于软件优化,Cache是有比较大的影响的。

Cache在物理上就是一块高速SRAM,ARM9E的Cache组织宽度(cache line)都是4个word(也就是32个字节);Cache的行为受系统控制器控制而不是程序员,系统控制器会把最近访问存储器地址附近的内容复制到Cache中去,这样,当CPU访问下一个存储器单元的时候(这个访问既可能是取指,也可能是数据),可能这个存储器单元的内容已经在Cache里了,所以CPU不需要真的到主存储器上去读取内容,而直接读取Cache高速缓存上面的内容就可以了,从而加快了访问的速度。

从Cache的工作原理我们可以看 到,其实Cache的调度是基于概率的,CPU要访问的数据既可能在Cache中已经存在(Cache hit),也可能没有存在(Cache miss)。在Cache miss的情况下,CPU访问存储器的速度会比没有Cache的情况更坏,因为CPU除了要从存储器访问数据以外,还需要处理Cache hit或miss的判断,以及Cache内容的刷新等动作。

只有当Cache hit带来的好处超过Cache miss带来的牺牲的时候,系统的整体性能才能得到提高,所以Cache的命中率成为一个非常重要的优化指标。

根据Cache行为的特点,我们可以直观地得到提高Cache命中率的一些方法,如尽可能把功能相关的代码和数据放置在一起,减少跳转次数;跳转经常会引起 Cache miss。保持合适的函数大小,不要书写太多过小的函数体,因为线性的程序执行流程是最为Cache友好的。

循环体最好放置在4个word对齐的地址,这 样就能保证循环体在Cache中是行对齐的,并且占用最少的Cache行数,使得被多次调用的循环体得到更好的执行效率。

6

性能和效率的提升

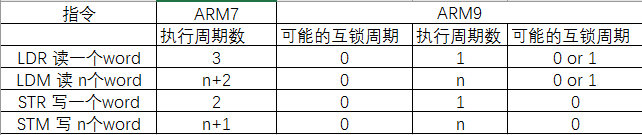

前面介绍了ARM9E相比于ARM7性能上的提高,这不仅表现在ARM9E有更快的主频、更多的硬件特性上面,还体现在某些指令的执行效率上面。执行效率我 们可以用CPU的时钟周期数(Cycle)来衡量;

运行同一段程序,ARM9E的处理器可以比ARM7节省大约30%左右的时钟周期。

效率的提高主要来自于ARM9E对于Load-Store指令执行效率的增强。我们知道在RISC架构的处理器中,程序中大约有30%的指令是Load- Store指令,这些指令的效率对系统效率的贡献是最明显的。

ARM9E中有两个因素帮助提高Load-Store指令的效率:

1)ARM9内核是哈佛架构,拥有独立的指令和数据总线;相对应,ARM7内核的指令和数据总线复用的冯诺依曼架构。

2)ARM9的5级流水线设计把存储器访问和寄存器写回放在不同的流水上面。

两者结合,使得在指令流的执行过程中每个CPU时钟周期都可以完成一个Load或Store指令。

下面的表格比较了ARM7和ARM9处理器之间的Load -Store指令。

从中可以看出所有的Store指令ARM9比ARM7省1个周期,Load指令可以省2个周期(在没有互锁的情况下,编译工具能够通过 编译优化消除大多数的互锁可能)。

综合各种因素,ARM9E处理器拥有非常强大的性能。但是在实际的系统设计中,设计人员并不总是把处理器性能开到最大,理想情况是把处理器和系统运行频率降低,使得性能刚好能满足应用需求; 达到节省功耗和成本的目的。

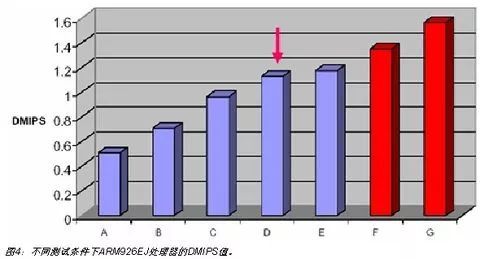

在评估系统能够提供的处理器能力过程中,DMIPS指标被很多人采用; 同时它也被广泛应用于不同处理器间的性能比较。

但是用DMIPS来衡量处理器性能存在很大的缺陷。 DMIPS并非字面上每秒百万条指令的意思,它是一个测量CPU运行一个叫Dhrystone的测试程序时表现出来的相对性能高低的一个单位(很多场合人们也习惯用MIPS作为这个性能指标的单位)。因为基于程序的测试容易受到恶意优化的干扰,并且DMIPS指标值的发布不受任何机构的监督,所以使用DMIPS进行评估时要慎重。

例如对Dhrystone测试程序进行不同的编译处理,在同一个处理器上运行也可以得出差别很大的结果。

DMIPS另外一个缺点是不能测量处理器的数字信号处理能力和Cache/MMU子系统的性能。因为Dhrystone测试程序不包含DSP表达式,只包含一些整型运算和字符串处理,并且测试程序偏小,几乎可以完整地放在Cache里面运行而无需与外部存储器进行交互。这样就难以反映处理器在一个真实系统中的真正性 能。

一种值得鼓励的评估方法是站在系统的角度看问题,而不仅仅拘泥于CPU本身;而系统性能评估最好的测试向量就是用户应用程序或相近的测试程序,这是用户所需的最真实的结果。

7

ARM9E处理器的DSP运算能力

伴随应用程序的多样化和复杂化,诸如多媒体、音视频功能在嵌入式系统里面也是全面开花。这些应用需要相当的DSP处理能力;如果是在传统的RISC架构上实 现这些算法,所需的资源(频率和存储器等)会非常不经济。

ARM9E处理器一个非常重要的优势就是拥有轻量级的DSP处理能力,以非常小的成本(CPU增 加功能需要增加硬件)换来了非常实用的DSP性能。

因为CPU的DSP能力并不直接反映在像DMIPS这样的评测指标中,同时像以前的ARM7处理器中也没有类似的概念;所以这一点对所有使用ARM9E处理器进行开发的人来说,都是需要注意的一个要点。

ARM9E的DSP扩展指令,主要包括三个类型:

1)单周期的16x16和32x16 MAC操作,因为数字信号处理中甚少32位宽的操作数,在32位寄存器中可以对操作数分段运算显得非常有用。

2)对原有的算术运算指令增加了饱和处理扩展,所谓饱和运算,就是当运算结果大于一个上限或小于一个下限时,结果就等于上限或是下限;

饱和处理在音频数据和视频像素处理中普遍使用,现在一条单周期饱和运算指令就能够完成普通RISC指令“运算-判断-取值”这一系列操作。

3)前导零(CLZ)运算指令,提高了归一化和浮点运算以及除法操作的性能。

以流行的MP3解码程序为例。整个解码过程中前端的三个步骤是运算量最大的,包括比特流的读入(解包)、霍夫曼译码还有反量化采样(逆变换)。

ARM9E的 DSP指令正好可以高效地完成这些运算。以44.1 KHz@128 kbps码率的MP3音乐文件为例,ARM7TDMI需要占用20MHz以上的资源,

而ARM926EJ则只要小于10MHz的资源在从ARM7到ARM9的平台转变过程中,有一件事情是非常值得庆幸的,即ARM9E能够完全地向后兼容ARM7上的软件;并且开发人员面对的编程模型和架构基础也保持一致。

但是毕竟ARM9E中增加了很多新的特性,为了充分利用这些新的资源,把系统性能优化好,需要我们对ARM9E做更多深入地了解。

---end--

6月中旬来了,有同学询问我们的淘宝店铺是否搞降价活动,这里统一回复:产品定价已经很亲民,我们不打价格战,和往年一样,不参加618大促,目前只有现金奖励活动(点击下面标题了解详情):

【有奖活动】完成课后作业:裸机测试界面, 赢取奖金2000元人民币,

按要求完成最高可获得2000元现金奖励~,适合时间充裕还可以赚外快补贴生活费的在校生,何乐而不为?

41人加群,据小编了解目前已有好几个人正在写代码...你还在等什么?

免责声明:本文系网络转载,有改动,版权归原作者所有。如涉及作品版权问题,请与我们联系,我们将根据您提供的版权证明材料确认版权并支付稿酬或者删除内容。

ARM7简介

ARM7系列处理器是英国ARM公司设计的主流嵌入式处理器ARM7内核是0.9MIPS/MHz的三级流水线和冯·诺伊曼结构;ARM9内核是5级流水线,提供1.1MIPS/MHz的哈佛结构。ARM7没有MMU。

ARM7系列包括ARM7TDMI、ARM7TDMI-S、带有高速缓存处理器宏单元的ARM720T。该系列处理器提供Thumb16位压缩指令集和EmbededICE软件调试方式,适用于更大规模的SoC设计中。ARM7TDMI基于ARM体系结构V4版本,是目前低端的ARM核。

ARM7TDMI处理器是ARM通用32位微处理器家族的成员之一。它具有优异的性能,但功耗却很低,使用门的数量也很少。它属于精简指令集计算机(RISC),比复杂指令集计算机(CISC)要简单得多。这样的简化实现了:高的指令吞吐量;出色的实时中断响应;小的、高性价比的处理器宏单元。三级流水线:ARM7TDMI处理器使用流水线来增加处理器指令流的速度。这样可使几个操作同时进行,并使处理和存储器系统连续操作,能提供0.9MIPS/MHz的指令执行速度。ARM7TDMI的流水线分3级,分别为:取指、译码、执行。正常操作过程中,在执行一条指令的同时对下一条指令进行译码,并将第三条指令从存储器中取出。内同时有5个指令在执行。在同样的加工工艺下,ARM9TDMI处理器的时钟频率是ARM7TDMI的1.8~2.2倍。

ARM9简介

ARM9系列处理器是英国ARM公司设计的主流嵌入式处理器,主要包括ARM9TDMI和ARM9E-S等系列。

ARM9采用哈佛体系结构,指令和数据分属不同的总线,可以并行处理。在流水线上,ARM7是三级流水线,ARM9是五级流水线。由于结构不同,ARM7的执行效率低于ARM9。平时所说的ARM7、ARM9实际上指的是ARM7TDMI、ARM9TDMI软核,这种处理器软核并不带有MMU和cache,不能够运行诸如linux这样的嵌入式操作系统。而ARM公司对这种架构进行了扩展,所以有了ARM710T、ARM720T、ARM920T、ARM922T等带有MMU和cache的处理器内核。

ARM9处理能力

(1)时钟频率的提高

ARM7处理器采用3级流水线,而ARM9采用5级流水线。增加的流水线设计提高了时钟频率和并行处理能力。5级流水线能够将每一个指令处理分配到5个时钟周期内,在每一个时钟周期内同时有5个指令在执行。在同样的加工工艺下,ARM9TDMI处理器的时钟频率是ARM7TDMI的1.8~2.2倍。

(2)指令周期的改进

指令周期的改进对于处理器性能的提高有很大的帮助。性能提高的幅度依赖于代码执行时指令的重叠,这实际上是程序本身的问题。对于采用最高级的语言,一般来说,性能的提高在30%左右。

UCOS简介

μC/OS II(Micro-Controller OperaTIng System Two)是一个可以基于ROM运行的、可裁剪的、抢占式、实时多任务内核,具有高度可移植性,特别适合于微处理器和控制器,适合很多商业操作系统性能相当的实时操作系统(RTOS)。为了提供最好的移植性能,μC/OS II最大程度上使用ANSI C语言进行开发,并且已经移植到近40多种处理器体系上,涵盖了从8位到64位各种CPU(包括DSP)。 μC/OS II可以简单的视为一个多任务调度器,在这个任务调度器之上完善并添加了和多任务操作系统相关的系统服务,如信号量、邮箱等。其主要特点有公开源代码,代码结构清晰、明了,注释详尽,组织有条理,可移植性好,可裁剪,可固化。内核属于抢占式,最多可以管理60个任务。从1992年开始,由于高度可靠性、鲁棒性和安全性,μC/OS II已经广泛使用在从照相机到航空电子产品的各种应用中。

μC/OS-II实时多任务操作系统内核。它被广泛应用于微处理器、微控制器和数字信号处理器。 μC/OS-II 的前身是μC/OS,最早出自于1992 年美国嵌入式系统专家Jean J.Labrosse 在《嵌入式系统编程》杂志的5 月和6 月刊上刊登的文章连载,并把μC/OS 的源码发布在该杂志的B B S 上。

UCOS应用情况

1) 高优先级的任务因为需要某种临界资源,主动请求挂起,让出处理器,此时将调度就绪状态的低优先级任务获得执行,这种调度也称为任务级的上下文切换。

2) 高优先级的任务因为时钟节拍到来,在时钟中断的处理程序中,内核发现高优先级任务获得了执行条件(如休眠的时钟到时),则在中断态直接切换到高优先级任务执行。这种调度也称为中断级的上下文切换。 这两种调度方式在μC/OS-II的执行过程中非常普遍,一般来说前者发生在系统服务中,后者发生在时钟中断的服务程序中。 调度工作的内容可以分为两部分:最高优先级任务的寻找和任务切换。其最高优先级任务的寻找是通过建立就绪任务表来实现的。μ C / O S 中的每一个任务都有独立的堆栈空间,并有一个称为任务控制块TCB(Task Control Block)的数据结构,其中第一个成员变量就是保存的任务堆栈指针。任务调度模块首先用变量OSTCBHighRdy 记录当前最高级就绪任务的TCB 地址,然后调用OS_TASK_SW函数来进行任务切换。

ARM9系列处理器是英国ARM公司设计的主流嵌入式处理器,主要包括ARM9TDMI和ARM9E-S等系列。

- 相关百科

- 相关知识

- 相关专栏

- 建筑材料工程质量监督与验收丛书:建筑保温,吸声材料分册

- 主震

- 保温结构

- 韩力机械

- msp430开发板

- 分条设备

- 四点抗压试验机

- 连创工程机械

- 光磁共振法

- 朗兆

- 马耳他十字

- 俭牌节能灯

- 滚花高螺母

- 粗枝剪

- 大平剪

- IT-CEOZ0JD-A

- 基于超磁致伸缩效应的新型液压高速开关阀

- 高效率PWM/PFM自动切换升压转换器的设计

- 影响免蒸养(压)粉煤灰小型空心砌块强度指标的因素

- 圆CFRP-钢管混凝土轴压短柱荷载-变形关系分析

- 影响沥青混凝土路面压实效果的主要因素及采取的对策

- 中国报告网十三五期间中国电解铝工业发展环境分析

- 永久性混凝土模板—快易收口网应用与施工技术

- 圆筒仓方筒仓液压滑模施工中倾斜与扭转的特征及对策

- 榆横煤化工业园区水资源的保护利压与可持续发展分析

- 在高压输电线路杆塔加挂ADSS光缆应注意几个问题

- 中国热水管道增压泵价格行业十大立式自吸泵品牌首选

- 意大利EUROSWITCH压差开关压差堵塞指示器

- 基于升压DC-DC变换器的白光LED驱动芯片

- 择压法检测砌筑砂浆抗压强度技术规程召开编制组会议

- 中国电机工程学会高压专委会

- 以色列ELI自清洗网式过滤器和浅层介质过滤器简介