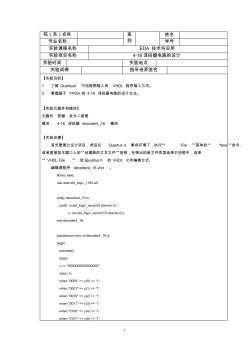

1 院(系)名称 班 别 姓名 专业名称 学号 实验课程名称 EDA 技术与应用 实验项目名称 4-16译码器电路的设计 实验时间 实验地点 实验成绩 指导老师签名 【实验目的】 1. 了解 QuartusII 中电路图输入和 VHDL 程序输入方式。 2. 掌握基于 FPGA 的 4-16 译码器电路的设计方法。 【实验元器件和模块】 元器件:按键、发光二极管 模块: 4-16 译码器 decoder4_16 模块 【实验步骤】 首先要建立设计项目,然后在 Quartus II 集成环境下,执行“ File ”菜单的“ New”命令, 或者直接按主窗口上的“创建新的文本文件”按钮,在弹出的新文件类型选择对话框中,选择 “ VHDL File ”,进入Quartus II 的 VHDL 文本编辑方式。 编辑源程序 decoder4_16.vhd 。 library ieee; use

七段显示译码器相关专题

- 卡箍的量是怎么算出来的

- 卡箍工程量问题

- 卡箍件的计算问题

- 卡箍如何计算

- 卡箍与法兰有何区别

- 卡簧尺寸怎么量

- 卡普隆雨棚做什么检验批

- 卡套接头的选用标准

- 卡箍连接管道

- 卡簧钳的型号是多少

- 新型贴片式户外全彩LED显示屏用途的显示器件

- 基于DSP智能断路器主控制器显示模块设计与实现

- 杭州市就业管理服务局液晶显示屏采购项目投标技术文件

- 基于DSP与FPGA全姿态指引仪图形显示系统设计

- 户外LED广告显示屏钢结构工程施工制作标准

- 屏端子上加装码制转换盒实现主变压器分接开关位置显示

- LCD与LED液晶显示屏的区别

- 电梯彩色液晶楼层显示器

- 平板显示产品质量检测中心建设项目永久用电工程施工专业

- LG E2350V成为全球首款UL环境认证LED显示器

- P8户外表贴LED电子显示屏户外P8全彩LED大屏幕

- LED显示屏无线GPRS控制方案

- XCQN2系列感应式高压带电显示装置使用说明书

- LED控制卡软件操作手册LED显示屏控制卡软件操作手册

- 分辨率为的硅基OLED微显示驱动芯片设计

- 多功能报告厅室内全彩P2.5LED显示屏技术参数、要求

- 42寸OLED显示屏驱动编程指南程序说明书