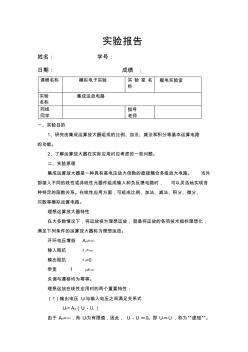

实验报告 姓名: 学号: 日期: 成绩 : 课程名称 模拟电子实验 实 验 室 名 称 模电实验室 实验 名称 集成运放电路 同组 同学 指导 老师 一、实验目的 1、研究由集成运算放大器组成的比例、加法、减法和积分等基本运算电路 的功能。 2、了解运算放大器在实际应用时应考虑的一些问题。 二、实验原理 集成运算放大器是一种具有高电压放大倍数的直接耦合多级放大电路。 当外 部接入不同的线性或非线性元器件组成输入和负反馈电路时, 可以灵活地实现各 种特定的函数关系。在线性应用方面,可组成比例、加法、减法、积分、微分、 对数等模拟运算电路。 理想运算放大器特性 在大多数情况下,将运放视为理想运放,就是将运放的各项技术指标理想化, 满足下列条件的运算放大器称为理想运放。 开环电压增益 Aud=∞ 输入阻抗 r i =∞ 输出阻抗 r o=0 带宽 f BW=∞ 失调与漂移均

热门知识

集成运放电路分析-

话题: 地产家居yangwenjian

精华知识

集成运放电路分析-

话题: 电气工程hanhengchun

-

话题: 地产家居wkfeng2005

最新知识

集成运放电路分析-

话题: 工程造价speedup007

集成运放电路分析相关专题

- 综合弱电集成包含哪些

- 集成电路板是怎么制作的

- 集成电路查询有哪些网站

- 集成电路查询网

- 集成块的电源

- 集成稳压电源的优点是什么

- 集成块CD2822A各脚的电压值

- 集成稳压电源电路中问题

- 简单无线电集成块/PCB

- 同或门的集成电路

- 分形DGS单元结构设计及其在微带电路中的应用

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 中国工程图学学会成立工程与制造系统集成化分会

- 中国吹制玻璃行业市场前景分析预测年度报告(目录)

- 中国电力井盖行业市场前景分析预测年度报告(目录)

- 中国轨道射灯行业市场前景分析预测年度报告

- 智能磨音频谱分析仪(DF-6811A)使用说明书

- 园林绿化养护精细化管理对河源市园林景观的影响分析

- 中国水电路桥武邵高速公路六标项目质量检验试验计划

- 中国民宿消费市场格局分析及十三五发展环境分析报告

- 圆CFRP-钢管混凝土偏压构件荷载-变形关系分析

- 云计算对企业信息化系统建设和运营的影响分析和改进

- 中国仿古青砖行业市场前景分析预测年度报告(目录)

- 智能建筑工程设计中的机电设备集成配置系统总体设计

- 在8度地震区建造低层纯钢框架结构住宅的可行性分析

- 中国家具钢管行业市场前景分析预测年度报告(目录)

- 中国电动汽车充电站市场现状与投资分析报告