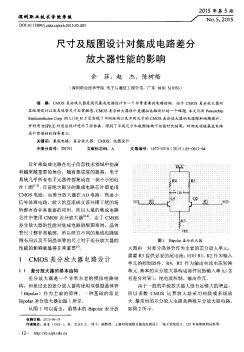

CMOS差分放大器是现代集成电路设计中一个非常重要的电路结构.由于CMOS差分放大器对其版图设计以及晶体管尺寸非常敏感,CMOS差分放大器设计是模拟电路设计的一个难题.本文利用PowerchipSemiconductorCorp的L110-N工艺实现了不同结构以及不同尺寸的CMOS差分放大器的电路图和版图设计,并利用HSPICE对这些设计进行了后仿真,得到了不同尺寸和版图结构下性能对比结果,对相关领域集成电路设计有很好的指导意义.

热门知识

差分放大器-

话题: 电气工程qq573539050

-

话题: 电气工程kai555yong

-

话题: 工程造价zclizhiguo

精华知识

差分放大器-

话题: 工程造价huangxinut

-

话题: 工程造价chris_paulcs

最新知识

差分放大器-

话题: 地产家居wanghaiyan

-

话题: 工程造价hengdi0769

-

话题: 工程造价xx5051856218

差分放大器相关专题

- 卡米亚瓷砖质量差

- 开关IP2P3P是怎么分的

- 开关多控与双控有什么差别

- 抗渗混凝土P8怎么调差

- 空气开关的级别可分哪几种

- 矿棉板吊顶隐框与明框价差

- 矿棉与岩棉有差价

- 框架梁和非框架梁怎么分

- 框架梁如何分梁跨

- 徕卡m-p为什么报价差距好大

- 尺寸及版图设计对集成电路差分放大器性能的影响

- 基于压电堆驱动器的喷嘴挡板式气体控制阀

- 电气工程及其自动化特色专业建设探索

- 分形DGS单元结构设计及其在微带电路中的应用

- 磷铵技术改造五大磷肥工程的建议

- 以大豆油多元醇制备的硬质聚氨酯泡沫塑料的性能

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 预制砌块(砖、石)挡土墙工程砌体施工安全技术交底

- 应用模糊数学理论对公路工程建设项目方案的综合评价

- 引嫩工程扩建区土壤水盐动态与防治土壤盐碱措施

- 中华华丹雨、污水管道沟槽开挖专项施工方案教学教材

- 中国工程图学学会成立工程与制造系统集成化分会

- 中国吹制玻璃行业市场前景分析预测年度报告(目录)

- 可替代现有隔热保温材料的新型材料

- 医院病房楼工程施工装饰装修工程施工控制

- 在生活中构筑自然——河南天旺园林工程有限公司剪影

- 中国机械工程学会授予材料热处理工程师资格人员名单